# Prozessortechnik - Mikrocomputertechnik 3

Vorlesung und Übungen

mit Seminaraufgaben

Ausgabe 0.2, 23.11.2015 Autor: Stephan Rupp

# Inhaltsverzeichnis

| 1.                  | Serielle Schnittstellen           |                                             |    |  |  |  |  |  |

|---------------------|-----------------------------------|---------------------------------------------|----|--|--|--|--|--|

|                     | 2.                                | SPI - Serielle Schnittstelle für Peripherie | 5  |  |  |  |  |  |

|                     | 3.                                | I2C Bus                                     | 14 |  |  |  |  |  |

|                     | 4.                                | USB                                         | 17 |  |  |  |  |  |

| 5.                  | Signalverarbeitung                |                                             |    |  |  |  |  |  |

|                     | 6.                                | Signale und Variablen in HDL                | 17 |  |  |  |  |  |

|                     | 7.                                | FIR Filter                                  | 21 |  |  |  |  |  |

|                     | 8.                                | Steuerwerk für das FIR Filter               | 29 |  |  |  |  |  |

| 9.                  | Mikroprozessoren                  |                                             |    |  |  |  |  |  |

|                     | 10.                               | Prozessorarchitektur                        | 44 |  |  |  |  |  |

|                     | 11.                               | Implementierung der Prozessorarchitektur    | 47 |  |  |  |  |  |

|                     | 12.                               | Ablauf der einzelnen Befehle                | 53 |  |  |  |  |  |

|                     | 13.                               | Programme mit Sprungbefehlen                | 58 |  |  |  |  |  |

|                     | 14.                               | Implementierung in HDL                      | 61 |  |  |  |  |  |

|                     | 15.                               | Tests                                       | 64 |  |  |  |  |  |

| 16.                 | Erweiterungen des Mikroprozessors |                                             |    |  |  |  |  |  |

|                     | 17.                               | Unterprogramme                              | 65 |  |  |  |  |  |

|                     | 18.                               | Unterbrechungssystem                        | 74 |  |  |  |  |  |

|                     | 19.                               | Ports für Geräte                            | 74 |  |  |  |  |  |

|                     | 20.                               | Timer                                       | 74 |  |  |  |  |  |

|                     | 21.                               | Serielle Schnittstellen                     | 74 |  |  |  |  |  |

| 22.                 | Signalprozessoren                 |                                             |    |  |  |  |  |  |

|                     | 23.                               | Architektur                                 | 74 |  |  |  |  |  |

|                     | 24.                               | Parallelverarbeitung                        | 78 |  |  |  |  |  |

|                     | 25.                               | Gleitkomma-Arithmetik                       | 87 |  |  |  |  |  |

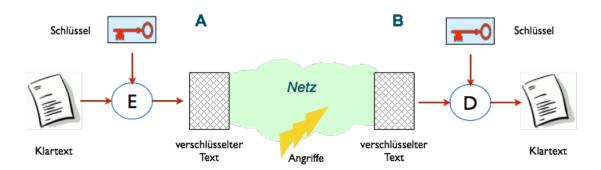

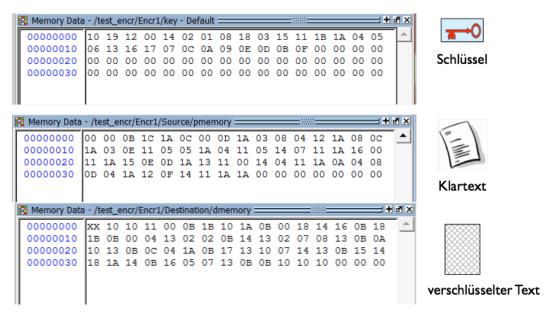

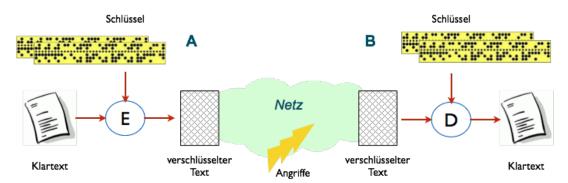

| 26. Verschlüsselung |                                   |                                             |    |  |  |  |  |  |

|     | 27.                                | 27. Die Pfadfindermethode                       |     |  |  |  |  |  |

|-----|------------------------------------|-------------------------------------------------|-----|--|--|--|--|--|

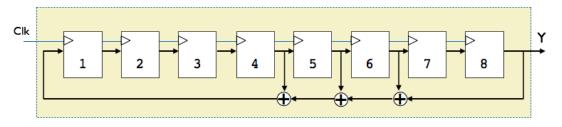

|     | 28.                                | Stromziffern                                    | 93  |  |  |  |  |  |

|     | 29.                                | Prüfsummen                                      | 96  |  |  |  |  |  |

|     | 30.                                | AES                                             | 98  |  |  |  |  |  |

|     | 31.                                | Angriffe mit roher Gewalt                       | 98  |  |  |  |  |  |

| 32. | Netzwerk                           |                                                 |     |  |  |  |  |  |

| 33. | Übu                                | Übungsaufgaben                                  |     |  |  |  |  |  |

|     | 34.                                | Zustandsautomat für die serielle Schnittstelle  |     |  |  |  |  |  |

|     | 35.                                | Zustandsautomat für das FIR Filter              | 103 |  |  |  |  |  |

|     | 36. Prozessor mit Akku-Architektur |                                                 |     |  |  |  |  |  |

|     | 37.                                | Prozessor mit Register-Architektur              | 111 |  |  |  |  |  |

|     | 38.                                | Erweiterungen des Prozessors (Akku-Architektur) | 112 |  |  |  |  |  |

# 1. Serielle Schnittstellen

Serielle Schnittstellen haben parallele Bussysteme zunehmend abgelöst. Grund hierfür ist die Möglichkeit der Einsparung vieler Anschlusskontakte an den Bausteinen, sowie der hiermit verbundene Aufwand für Leitungen. Die für die serielle Verbindung erforderlichen hohen Datenraten sind keine technische Herausforderung mehr. Im Unterschied zu Parallelbussystemen vermeidet die serielle Übertragung Laufzeitunterschiede zwischen den einzelnen Signalen. Daher sind serielle Schnittstellen in der Praxis leistungsfähiger als Parallelbussysteme. Ein Beispiel hierfür ist die Ablösung von PCI durch PCI-Express auf Mikroprozessorsystemen. In diesem Abschnitt werden einfache serielle Schnittstellen zur Anbindung von Schnittstellenmodulen an FPGAs näher beschrieben.

# 1.1. SPI - Serielle Schnittstelle für Peripherie

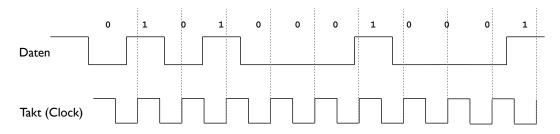

Das Serial Peripheral Interface (SPI) ist ein synchrones serielles Protokoll zur Kommunikation eines Mikrocontrollers mit peripheren Geräten. Mit serieller Kommunikation ist gemeint, dass die Daten nacheinander über eine gemeinsames Medium geschickt werden, im Unterschied zur parallelen Kommunikation. Synchrone Kommunikation bedeutet, dass Sender und Empfänger hierbei synchron arbeiten. In der Praxis wird hierzu eine Taktleitung verwendet. Folgende Abbildung zeigt das Prinzip der synchronen seriellen Kommunikation.

Bild 1.1 Synchrone serielle Kommunikation

Für die Daten ist eines der Systeme der Sender, das benachbarte System der Empfänger. Mit Hilfe des Taktes werden die Zeitpunkte definiert, an denen die Daten gültig sind und der Empfänger jeweils ein Datum übernehmen kann. Hierzu lassen sich z.B. die ansteigenden Flanken des Taktes verwenden, wie in der Abbildung gezeigt. Wer die Taktleitung betreibt, spielt für das Konzept keine Rolle. Allerdings muss es eine Stelle geben, die den Takt bereit stellt und die Kommunikation steuert.

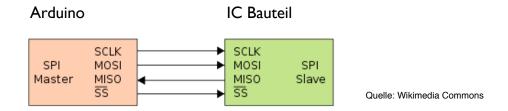

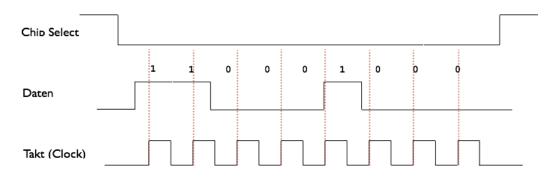

Nach diesem Konzept werden also für eine bidirektionale Kommunikation zwischen Sender und Empfänger drei Leitungen benötigt: (1) die Taktleitung, (2) eine Leitung zum Senden, (3) eine Leitung zum Empfangen. Auf diese Weise miteinander verbundene Komponenten würden also Daten austauschen, solange ein Taktsignal gegeben wird. Gibt es mehr als zwei Kommunikationspartner, lässt sich der jeweils gewünschte Baustein durch ein weiteres signal auswählen. Bei SPI ist diese Auswahl durch eine weitere Leitung gelöst, wir in folgender Abbildung dargestellt.

Bild 1.2 SPI als Kommunikationsschnittstelle

In der Abbildung zu sehen sind die bereits beschriebene Taktleitung (SCLK für SPI Clock), sowie die Datenleitungen in Senderichtung (MOSI für Master Out - Slave In), die Datenleitung in Empfangsrichtung (MISO für Master In - Slave Out). Die vierte Leitung ist mit SS bezeichnet für System Select (bzw. auch etwas neutraler als CS für Chip Select). Der Oberstrich auf der Bezeichnung ist als boolsche Negation zu interpretieren und bedeutet, dass das System durch den logischen Zustand LOW selektiert wird (als sogenannten active low Leitung).

Bild 1.3 Ablauf der Kommunikation mit Hilfe der Chip Select Leitung

Eines der beiden Systeme muss die Taktleitung betreiben und die Kommunikation über die Chip Select Leitung organisieren. Diese Funktion ist als Master bezeichnet und ist in der Regel die Rolle des Mikrocontrollers. Die Bezeichnungen der beiden Datenleitungen beziehen sich auf dem Master der Kommunikation. Aus Sicht der Bauteile sind die Bezeichnungen jeweils DI (für Data In) oder SDI (für Serial Data In) bzw. DO (für Data Out) oder SDO (für Serial Data Out).

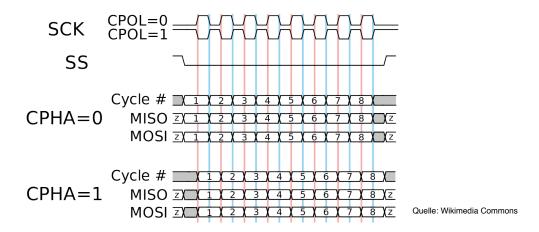

Die SPI-Spezifikation lässt Freiheitsgrade in der Interpretation des aktiven Taktsignals (Ruhewert bei LOW oder Ruhewert bei HIGH), sowie in der Wahl der aktiven Taktflanke (lesen der Daten bei steigender oder bei fallender Flanke). Hierzu tauchen also folgende Begriffe im Zusammenhang mit der SPI-Schnittstelle auf: CPOL (Clock Polarity) und CPHA (Clock Phase). Die vier kombinatorischen Möglichkeiten stellen die möglichen Betriebsmodi der Schnittstelle dar. Die folgende Übersicht verdeutlicht die Begriffe und den Zusammenhang.

Bild 1.4 Betriebsmodi der SPI-Schnittstelle

Weitere Protokolldefinitionen sind Sache des Herstellers von SPI Bausteinen. Hierzu gehört die Organisation der Daten für die Konfiguration des Bausteins (durch Setzen von Registern), die Datenformate für den Austausch von Informationen, die Organisation der Daten in Bytes, ggf. Quittungsnachrichten etc. Das generelle Vorgehen ist dabei immer gleich: (1) den Baustein konfigurieren, (2) Daten austauschen. Welche genauen Informationen in welchem Format benötigt werden findet sich im Datenblatt des Herstellers.

# Ansteuerung der SPI Schnittstelle

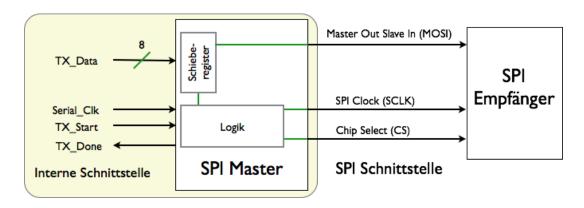

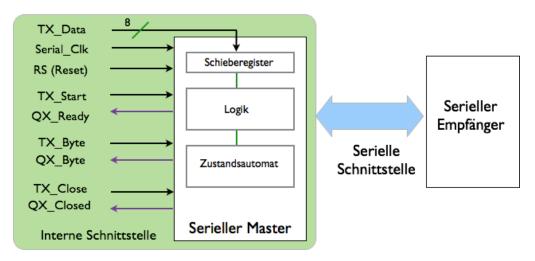

Bei der Erstellung eines Konzepts für die SPI-Schnittstelle ist ein Blockschaltbild hilfreich. Hierbei sind zu unterscheiden die externe Schnittstelle der Schaltung, d.h. der SPI-Bus, sowie die interne Schnittstelle der Schaltung zu einem eigenen, übergeordneten Block bzw. Programm. Die externe Schnittstelle ist hierbei vorgegeben: für einen SPI Master, der Daten an einen SPI-Empfänger überträgt, gehören hierzu die Signale MOSI (die serielle Datenleitung zum Empfänger), die SPI-Clock (SCLK) zum Eintakten der Bots in dem Empfänger, sowie das Chip Select-Signal (CS), das den Empfänger aktiviert. Die folgende Abbildung zeigt eine solche Anordnung.

Bild 1.5 Blockdiagramm zur Orientierung

Die Schnittstelle zu einer Schaltung, die den SPI-Master bedient, ist hierbei eine interne Schnittstelle in dem Sinne, dass die Gestaltung völlig frei ist. Im in der Abbildung gezeigten Beispiel

wurden hierfür folgende Signale gewählt: Ein Byte an Daten (TX\_Data), das parallel in den SPI-Master übertragen wird. Der SPI-Master überträgt diese Daten dann seriell über die SPI-Schnittstelle. Das Startsignal zur Übertragung (TX-Start) aktiviert die serielle Übertragung. Sobald die serielle Übertragung beendet ist, schickt der SPI-Master als Quittung das Signal TX\_Done. Dem SPI-Master wird eine Takt zur seriellen Übertragung bereitgestellt: Serial\_Clk.

Aus dieser Anordnung ergibt sich dann folgender Ablauf für den SPI-Master: (1) Beim Startsignal TX\_Start mit der Übertragung der im Schieberegister enthaltenen Daten beginnen. (2) Übertragung: Hierzu erzeugt der SPI-Master das Chip-Select (CS) Signal für den SPI-Empfänger. Der SPI-Master zählt die benötigten Anzahl Takte mit und erzeugt eine passende Anzahl Takte (SCLK) für den Empfänger. (3) Das Ende der Übertragung signalisiert der SPI-Master mit Hilfe des Signals TX\_Done. Folgender Programmtext beschreibt eine mögliche Realisierung.

```

library IEEE;

use IEEE.STD LOGIC 1164.ALL;

use IEEE.NUMERIC STD.ALL;

-- Settings:

-- SPI-Mode 0: CPOL=0, CPHA=0

-- Serial Clk : serial clock as input for SPI Clock

-- SCLK: SPI Clock output to slave

entity SPI Master is

Port ( TX Data : in STD LOGIC VECTOR (7 downto 0); -- Transmit Register

TX_Start : in STD_LOGIC; -- Start Transmission

Serial_Clk : in STD_LOGIC; -- Serial clock in at SCLK rate

TX Done : out STD LOGIC; -- Handshake signal (transmission done)

MOSI : out STD_LOGIC; -- SPI Master out signal SCLK : out STD_LOGIC; -- SPI clock signal out SS : out STD_LOGIC -- SPI chip select signal

);

end SPI Master;

architecture RTL of SPI Master is

-- internal signals and variables

signal txreg : std_logic_vector(7 downto 0) := (others=>'0');

signal counter : integer := 0;

begin

-- start transaction with new sample

process(Serial Clk, TX Start) begin

if (rising_edge(TX_Start)) then

counter <= 8; -- initialize counter for 8 bits transmission (9 - 1)</pre>

TX Done <= '0'; -- initialize handshake signal to not done

SS <='0'; -- chip select is active low

SCLK <= '0'; -- SCLK operated in CPOL = 0 (active low, rising edge)</pre>

txreg <= TX Data;</pre>

```

```

elsif (TX Start = '1') then

if (falling edge(Serial Clk) and (counter > 0)) then

SCLK <= '0'; -- SCLK follows input SPI clock for 8 counts

MOSI <= txreq(7);

for i in 0 to 6 loop

txreg(7-i) \le txreg(6-i);

end loop;

elsif(rising edge(Serial Clk) and (counter > 0))then

SCLK <= '1'; -- SCLK follows input SPI clock for 8 counts

counter <= counter - 1;</pre>

end if;

if (counter = 0) then

TX Done <= '1'; -- handshake signal for transmission completed

SS <='1';

-- deselect chip

end if;

end if;

end process;

end RTL;

```

Bei dieser Implementierung wird die Synchronisation des SPI-Masters mit der internen Schnittstelle zur Steuerung des Datentransfers über SPI durch folgende Massnahmen erreicht: (1) Start der Übertragung durch Trägern auf die steigende Flanke des Steuersignals TX\_Start. In diesem Zustand wird dann auch das Chip-Select-Signal bedient, sowie ein interner Bitzähler counter gesetzt. (2) Solange TX-Start gesetzt bleibt, folgt der SPI-Master der seriellen Taktrate Ser\_Clk, überträgt jeweils ein Bit, erzeugt die SPI-Clock SCLK und zählt mit jedem Takt den Bitzähler herunter. Synchronität ist nur dadurch gewährleistet, dass die SPI-Clock aus dem Zustand Low gestartet wird, d.h. dass auf das Signal TX\_Start zunächst eine steigende Taktflanke der SPI-Clock SCLK folgen muss. Hierzu muss auf TX-Start zunächst eine fallende Flanke der seriellen Eingangstaktes Ser\_Clk folgen.

#### Testprogramm für den SPI Master

Zum Testen der Schaltung wird die interne Schnittstelle des SPI-Masters bedient. Diese Schnittstelle stellt die serielle Taktrate für die Übertragung bereit. Mit dem in der letzten Abbildung gewählten Konzept ist der Ablauf wie folgt: (1) Daten parallel in das Schieberegister des SPI-Masters schreiben. (2) Die Übertragung mit Hilfe des Startsignals TX-Start starten. (3) Auf das Ende der Übertragung warten (Signal TX\_Done des SPI-Masters). Nach der Sendebestätigung kann das nächste Byte übertragen werden. Folgender Programmtext beschreibt eine mögliche Realisierung.

```

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

USE ieee.numeric_std.ALL;

ENTITY test_SPI_Master IS

END test_SPI_Master;

```

```

ARCHITECTURE behaviour OF test spi master IS

-- Component Declaration for the Unit Under Test (UUT)

COMPONENT SPI Master

Port (TX Data: in STD LOGIC VECTOR (7 downto 0); -- Transmit Register

TX_Start : in STD_LOGIC; -- Start Transmission

Serial_Clk : in STD_LOGIC; -- serial clock in at SCLK rate

TX_Done : out STD_LOGIC; -- Handshake signal (transm. done)

MOSI : out STD_LOGIC; -- Master out signal

SCLK : out STD_LOGIC; -- SPI clock signal out

SS : out STD_LOGIC -- chip select signal

);

END COMPONENT;

-- Signals

SIGNAL T TX Data : std logic vector(7 downto 0) := (others=>'0');

SIGNAL T TX Start : std logic := '0';

SIGNAL T Serial Clk : std logic;

SIGNAL T_TX_Done : std_logic;

SIGNAL T_MOSI : std_logic;

SIGNAL T_SCLK : std_logic;

SIGNAL T_SS : std_logic;

SIGNAL rxreg : std logic vector(7 downto 0) := x"00";

BEGIN

-- Connect DUT to testbenck (port map)

DUT: SPI Master PORT MAP(

TX Data => T TX Data,

TX Start=> T TX Start,

Serial Clk => T Serial Clk,

TX Done => T TX Done,

MOSI => T MOSI,

SCLK

=> T SCLK,

SS

=> T SS

);

-- operate DUT

clock : process begin

T Serial CLK <= '1';

wait for 10 ns;

T Serial CLK <= '0';

wait for 10 ns;

end process clock;

test : process begin

T TX Data <= x"00"; -- transmit control byte

T TX Start <= '1';

wait until T TX Done ='1';

wait for 5 ns;

T_TX_Start <= '0';</pre>

```

```

wait for 50 ns;

T_TX_Data <= x"bb"; -- transmit data byte

T_TX_Start <= '1';

wait until T_TX_Done ='1';

wait for 5 ns;

T_TX_Start <= '0';

wait for 100 ns;

END PROCESS test;

END Behavior;</pre>

```

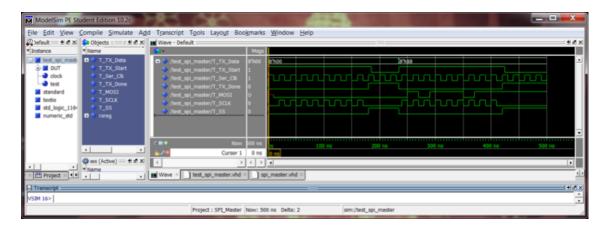

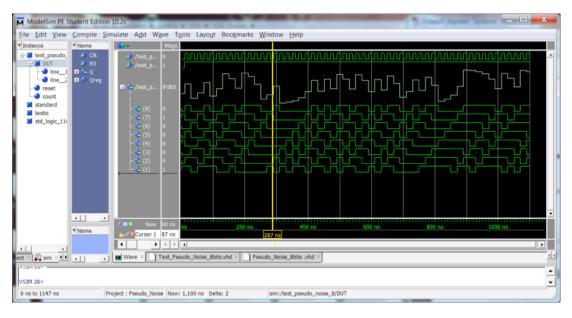

Das Textprogramm hat folgende parallele Prozesse: (1) Die Erzeugung des seriellen Taktes, (2) Die Übertragung zweier Bytes. In der gewählten Realisierung zählt der SPI-Master die seriell übertragenen Bits eigenständig mit und erzeugt selber das Chip-Select Signal. Folgende Abbildung zeigt den Test der Schaltung auf dem Simulator.

Bild 1.6 Test der SPI-Schnittstelle im Simulator

Man erkennt die Zustände der Datenleitung und kann jeweils 8 Taktsignale für den SPI-Clock (CSLK) abzählen. Ein Empfänger würde die Signale der Datenleitung mit jeder steigenden Flanke der SPI-Clock (CSLK) in sein Eingangs-Schieberegister einlesen. Am Ende jedes übertragenen Bytes setzt der SPI-Master das Chip-Select Signal (CS) eigenständig auf den inaktiven Zustand (High).

#### Ein praktisches Beispiel

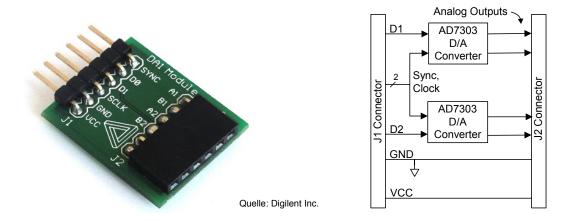

Als Beispiel sei ein D/A Wandler Modul gewählt, hier das PmodDA1 des Herstellers Digilent, das an der DHBW im Einsatz ist. Für eigene Experimente stellt Ihnen der Dozent gerne ein Exemplar zur Verfügung. Folgende Abbildung zeigt das Modul und das Blockschaltbild.

Bild 1.7 D/A Wandler Modul PmodDA1

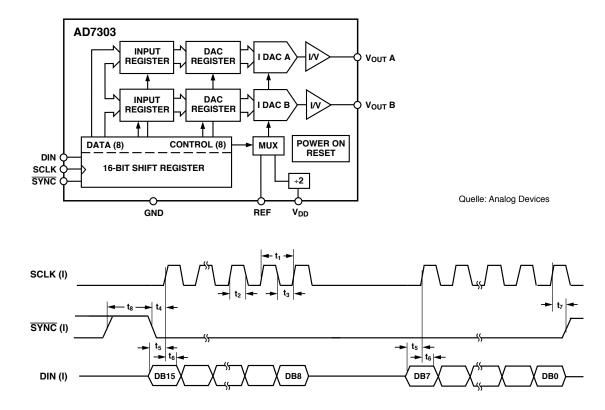

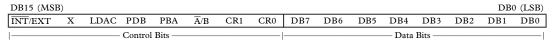

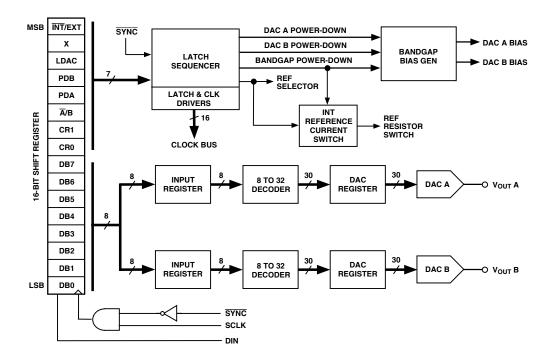

Auf dem Modul finden sich zwei D/A Wandler Bausteine AD7303. Der Weg führt also weiter zum Datenblatt des Herstellers Analog Devices. Dort findet sich das Blockschaltbild des Bausteins und ein Zeitdiagramm der SPI-Schnittstelle, wie in folgender Abbildung gezeigt.

Bild 1.8 Blockschaltbild und Zeitdiagramm des D/A Wandler Bausteins

Man erkennt, dass der Baustein zwei Bytes an Daten erwartet: (1) ein Kommando (Control mit 8 Bit) zur Steuerung der Betriebsart, (2) Daten (mit ebenfalls 8 Bit). Das Schieberegister am Eingang des Chips ist dementsprechend 16 Bit lang. Das höchstwertigste Bit DB15 wird zuerst gesendet, d.h. die Reihenfolge ist MSB-LSB. Ausserdem erkennt man am Zeitdiagramm, dass der Ruhezustand der Clock 0 ist und die aktive Flanke die ansteigende Flanke (entsprechend CPHA = 0). Der SPI-Modus wäre demnach 0.

Übung 1.1: Zum Betrieb an diesem Baustein wären 16-Bits zu übertragen, d.h. 2 Bytes zwischen zwei Chip-Select Signalen. Modifizieren Sie die Schaltung hierfür und testen Sie am Simulator.

Übung 1.2: Im Falle der Übermittlung von Abtastwerten an den D/A-Wandler wäre die Schaltung mit einer Frequenz für die Abtastwerte F<sub>sample</sub> zu betreiben, sowie mit einer Bit-Clock für die serielle Schnittstelle F<sub>serial</sub>. Das FPGA stellt eine Quarzclock F<sub>Qaurz</sub> zur Verfügung. Wie wären die beiden Takte sinnvoll hieraus zu gewinnen?

#### Einsatz eines Zustandsautomaten

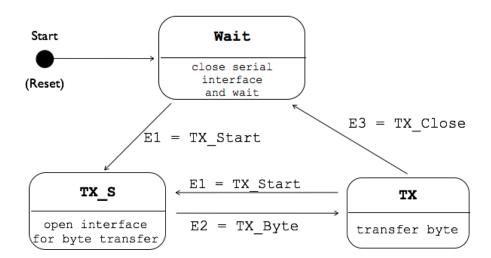

Die bisherige Implementierung kennt nur die Zustände Übertragung starten (mit Hilfe des Steuersignals TX\_Start). Nach dem Start wartet man auf das Quittungssignal TX\_Done, mit dem der SPI-Master das Ende der Übertragung anzeigt. Nach Ende der Übertragung befindet man sich in einem Wartezustand. Um die Übertragung mehrerer Bytes zu ermöglichen, sonn ein weiterer Zustand eingeführt werden: die Initialisierung des seriellen Busses mit Hilde des Chip-Select-Signals. Folgende Abbildung zeigt das Zustandsdiagramm des Automaten.

Bild 1.9 Zustandsdiagramm des Automaten zur Steuerung der Schnittstelle

Das Steuersignal TX\_Start führt nun vom Wartezustand in den Zustand der Initialisierung des seriellen Busses (TX\_S). Die Übertragung eines Bytes findet in diesem Zustand noch nicht statt, sondern wird durch ein weiteres Steuersignal TX\_Byte veranlasst, das in den Zustand der Übertragung (TX) führt. Nach Übertragung des Bytes aus dem Zustand TX lässt sich entweder (1) wiederum in den Zustand TX\_S wechseln (durch erneuten Senden des Steuersignals TXStart), (2) oder die Übertragung mit Hilfe des Steuersignals TX\_Close beenden. In diesem Fall wechselt der Automat in den Wartezustand Wait.

Zur Synchronisation der Steuerung soll der Automat aus jedem Zustand heraus Quittungen schicken, sobald er die jeweiligen Zustandsaktionen ausgeführt hat. Folgende Abbildung zeigt die erweiterte interne Schnittstelle des Automaten mit allen Steuersignalen und Quittungen. Hierbei wird das Steuersignal TX\_Start quittiert durch QX\_Ready (Automat hat Zugriff auf die seriellen Schnittstelle und ist bereit zur Übertragung), das Signal TX\_Byte wird quittiert durch QX\_Byte (Automat hat ein

S. Rupp, 2015 T2ELN3804, T2ELA3004.1 13/134

Byte übertragen), das Signal TX\_Close wird quittiert durch QX\_Closed (Automat hat die serielle Schnittstelle wieder freigegeben).

Bild 1.10 Blockdiagramm der erweiterten Steuerschnittstelle

Mit Hilfe dieser Vorgabe lässt sich nun ein Zustandsautomat zur Steuerung der Schnittstelle realisieren. Hierbei kann man der Vorgehensweise aus der Vorlesung Entwurf digitaler Systeme folgen (siehe (1) im Literaturverzeichnis).

Übung 1.3: Entwerfen Sie ein Testprogramm des Automaten, das die interne Schnittstelle bedient. Steuern Sie den Automaten so, dass mehrere Bytes übertragen werden.

Übung 1.4: Entwerfen Sie den Zustandsautomaten zur Steuerung der SPI-Schnittstelle. Hinweis: Die Implementierung der Schnittstelle kann im Ausgangsschaltwerk des Automaten erfolgen.

Übung 1.5: Testen Sie den Automaten mit Hilfe des im Übung 1.4 erstellten Testprogramms.

#### 1.2. I2C Bus

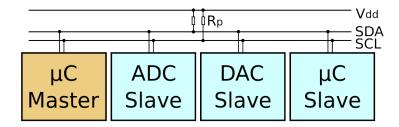

Während SPI insgesamt 4 Leitungen für eine bidirektionale Übertragung benötigt (bzw. 3 Leitungen für eine unidirektionale Übertragung), ist kommt der I²C Bus mit insgesamt 2 Leitungen aus. Den Unterschied macht die Adressierung der angeschlossenen Geräte: SPI benötigt für jedes Gerät am Controller (Master) eine eigene Adressleitung (Chip Select). I²C arbeitet mit Geräteadressen und benötigt daher keine eigene Leitung zur Auswahl eines Gerätes. Ausserdem wird nur eine einzige Datenleitung für beide Richtungen verwendet.

Ein I<sup>2</sup>C System hat die in folgender Abbildung gezeigte Struktur. Wegen der gemeinsamen Datenleitung spricht man hier auch von einer Bus-Struktur. Da die Schnittstelle seriell arbeitet, ist die Funktion der beiden Busleitungen eindeutig: eine der Leitungen ist die Taktleitung (SCL - Serial Clock Line), die andere Leitung ist die Datenleitung (SDA - Serial DAta Line).

Quelle: Wikimedia Commons

Bild 1.11 I2C Zweitdraht Bussystem

Den Nachrichtenaustausch steuert beim Zweidrahtbus I²C ebenfalls ein Master, in aller Regel der Mikrocontroller. Elektrisch haben alle angeschlossenen Bauteile offene Kollektorausgänge und sind über die Pull-up Widerstände an beiden Leitungen auf definiertem Potential. Dieser Anschluss stellt eine verdrahtete ODER-Verknüpfung der Ausgänge dar und wird zur Signalisierung benutzt. Hohe Datenraten sind bei diesem Konzept nicht vorgesehen. Die Taktrate liegt üblicherweise bei maximal 100 kHz im Standardmodus, bzw. bei maximal 400 kHz im sogenannten Fast Mode.

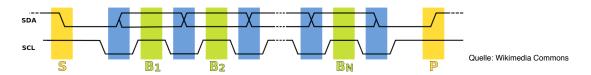

Für die Kommunikation gibt der Master den Takt vor. Das Protokoll gibt vor, dass jeweils Einheiten von 8 Bits übertragen werden. Bei der moderaten Taktrate lassen sich Phasenübergänge der Signale auf beiden Leitungen zur Steuerung der Kommunikation nutzen. Ein Startsignal gibt der Master durch eine fallende Flanke auf der Datenleitung, währen die Taktleitung noch im Ruhezustand ist (Ruhezustand = HIGH). Als Stopp-Signal zieht der Master die Datenleitung auf HIGH, nachdem die Taktleitung bereits in den Ruhezustand übergegangen ist. Folgende Abbildung zeigt den Ablauf der Kommunikation.

Bild 1.12 Kommunikation über den Zweidrahtbus I<sup>2</sup>C

Auffällig ist, dass Daten nicht bei fallenden oder steigenden Taktflanken interpretiert werden, sondern im Zustand HIGH der Taktleitung. Während dieses Zustandes dürfen sich die Daten auf der Datenleitung nicht ändern. Nach 8 Datenbits wird ein weiteres Protokollbit übertragen, das sogenannte Bestätigungsbit (Acknowledge Bit), das den Empfänger der Nachricht (vorausgegangene Bits) zu einer Quittierung des Empfangs motivieren soll. Wurde die Nachricht korrekt empfangen, legt der Empfänger die Datenleitung auf LOW und hält die Datenleitung in diesem Zustand während der folgenden HIGH Phase der Taktleitung. Die Taktleitung verbleibt in diesem Zustand (Ruhezustand). Der Übergang der Datenleitung in den Zustand LOW muss vor dem Übergang der Taktleitung in den Zustand HIGH erfolgen, um Missverständnisse zu vermeiden. Der Master hebt im Anschluss an die Interpretation der Quittung die Datenleitung auf HIGH und meldet hiermit das Stopp-Signal.

Wie werden nun Geräte adressiert? I<sup>2</sup>C verwendet üblicherweise 7-Bit Adressen, die im Byte Format als Nachricht verschickt werden. Das achte Bit kennzeichnet, ob die folgende Nachricht vom gewünschten Empfänger gelesen werden soll, oder ob der Empfänger eine Nachricht an den Master senden soll. Für Geräte, die entweder nur lesen oder nur schreiben können, spielt diese Unterscheidung allerdings keine Rolle. Die Geräteadressen werden vom Hersteller festgelegt, wobei

einige Adressbits vom Anwender durch Verdrahtung konfiguriert werden können, z.B. um mehrere baugleiche Geräte zu betreiben.

# Ein praktisches Beispiel

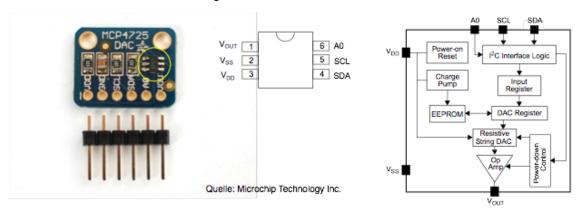

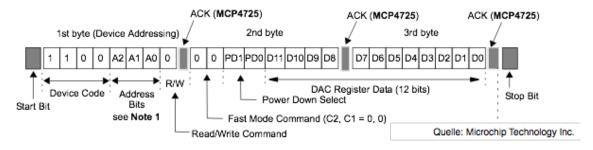

Als I²C Baustein soll der 12-Bit Digital-Analog-Konverter MCP4725 zum Einsatz kommen. Dem Datenblatt entnimmt man, dass der Baustein über eine Spannungsversorgung (V<sub>DD</sub>) mit Masse (V<sub>SS</sub>) verfügt, und das analoge Ausgangssignal (V<sub>OUT</sub>) herausgeführt wird. Die digitalen Abtastwerte werden über die I²C-Schnittstelle mit den Anschlüssen SCL und SDA angeschlossen. Ausserdem findet sich ein Eingang A0 zur Auswahl der Geräteadresse am I²C-Bus. Der Baustein kann im Standard Modus mit 100 kHz Datenrate, bzw. im sogenannten Fast-Mode mit 400 kHz Datenrate betrieben werden.

Bild 1.13 MCP4725 12-Bit DAC

Zum Speichern der Konfiguration (2 Bits), sowie der digitalen Eingangssignale (12-Bits) enthält der Baustein ein E-PROM. Die Konfiguration dient zum durch die Software gesteuerten Deaktivieren des Bausteins (Power-Down Modus), wobei der Ausgang auf unterschiedliche Impedanzen geschaltet werden kann. Ein DAC-Register ermöglich die Konfiguration des Übertragungsmodus am Bus. Hier enthalten sind 3 Bits zur Einstellung des Übertragungsmodus (Standard, Fast-Mode), ob das DAC-Register bzw. das EPROM beschrieben werden soll, bzw. ob das Statusbit (Ready/Busy) ausgelesen werden soll. Folgende Abbildung zeigt ein Beispiel für die Kommunikation.

Bild 1.14 Beispiel für die Kommunikation über die serielle Schnittstelle

Das erste übertragene Byte dient der Auswahl des Bausteins. Hierbei sind die Bits A2 und A1 der Adresse vom Hersteller fest voreingestellt (als Standard "00", bzw. auf Kundenwunsch), nur das Bit A0 wird durch die Beschaltung auf logisch Null oder Eins eingestellt. Die Konfigurationsdaten werden im zweiten Byte übertragen, zusammen mit den obersten 4 Bits des digitalen Signals. Mit einem dritten Byte endet die Übertragung eines Abtastwertes. Gemäß Spezifikation des I<sup>2</sup>C-Busses quittiert der Baustein die Übertragung im Anschluss an jedes Byte.

Seminararbeit S1: Erstellen Sie ein Konzept zur Anbindung eines I2C-Bausteins auf Ihrem FPGA. Erstellen Sie einen Schaltungsentwurf und Test Sie den Entwurf. Synthetisieren Sie die Schaltung und testen Sie die Implementierung. Für den Test stehen Ihnen DAC-Bausteine MCP4725 DAC zur Verfügung.

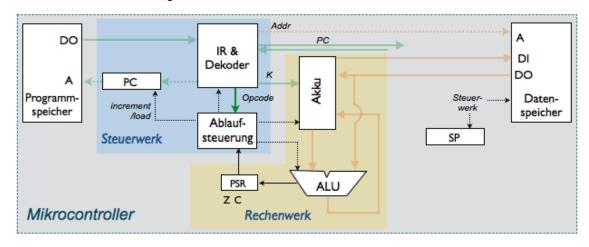

#### Emulation eines Mikrocontrollers

Bei den relativ bescheidenen Übertragungsraten von I<sup>2</sup>C lässt sich diese Schnittstelle auch durch Mikrocontroller bedienen, die man auf dem programmierbaren Baustein (FPGA) emuliert. Bei gängigen Mikrocontrollern finden sich in diesem Fall fertige Bibliotheken bzw. fertige HDL-Bausteine (IP - Intellectual Property) für solche Anwendungen. Die Emulation eines Mikrocontrollers auf FPGA ist Teil von Abschnitt 3 dieses Manuskripts.

#### 1.3. USB

Seminararbeit S2: Recherchieren Sie nach der Funktion und nach Realisierungsmöglichkeiten für eine USB-Schnittstelle auf Ihrem FPGA. Erstellen Sie ein Konzept. Erstellen Sie einen Schaltungsentwurf und Test Sie den Entwurf. Synthetisieren Sie die Schaltung und testen Sie die Implementierung durch Anbindung des FPGAs an Ihrem PC via USB.

# 2. Signalverarbeitung

# 2.1. Signale und Variablen in HDL

In der digitalen Signalverarbeitung werden Berechnungen in zeitdiskreten Systemen durchgeführt, wobei unter den Signalen die Abtastwerte bzw. die berechneten Werte verstanden werden. In diese Abschnitt geht es um Signale und Variablen als Schlüsselworte in VHDL. Beide können mit geeigneten Datentypen zur Signalverarbeitung eingesetzt werden. Signale in VHDL werden als globale Variablen verwendet, die über mehrere Prozesse hinweg sichtbar sind. Die sogenannten Variablen verwendet man als lokale Variablen innerhalb eines Prozesses. Folgende Beispiele sollen die Unterschiede im Gebrauch von Signalen und Variablen zeigen.

Übung 2.1: Analysieren Sie den HDL-Text. Welches Verhalten erwarten Sie von dieser Schaltung?

Übung 2.2: Schreiben Sie ein Testprogramm und testen Sie die Schaltung. Entspricht das Ergebnis Ihren Erwartungen?

Im gleichen HDL-Programm wird nun die Reihenfolge der Signalzuweisungen innerhalb des taktsensitiven Prozesses process (Clk) vertauscht:

```

process (Clk)

begin

if rising_edge(Clk) then

Qi(0) <= D;

Qi(1) <= Qi(0);

Qi(2) <= Qi(1);

end if;

end process;</pre>

```

Übung 2.3: Welches Verhalten erwarten Sie nun von der Schaltung?

Übung 2.4: Testen Sie die Schaltung mit dem Testprogramm aus Übung 1.7. Entspricht das Ergebnis Ihren Erwartungen? Erklären Sie, warum sich die Schaltung so verhält. Hinweise: (1) Der Prozess process (Clk) ist taktsensitiv und reagiert nur auf steigende Flanken. (2) Das Register Qi ist als Signal innerhalb des Architektur-Blocks der Entity prozessübergreifend definiert. Ein weiterer Prozess, der auf das Register zugreift, findet sich in der Zeile Q <= Qi(2).

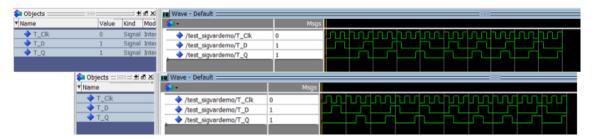

Beide Testläufe zeigen folgende Ergebnisse (das Testprogramm schreibt ein Muster 010 010 ... auf den Eingang des Prüflings):

#### Bild 2.1 Testläufe beider Varianten

In folgendem HDL-Text wird nun statt des Signals Qi eine Variable Vi mit identischem Datentyp (3-Bit breiter Vector) verwendet. Da die Variable nur innerhalb eines Prozesses Gültigkeit hat, wird sie im Prozessblock process (Clk) deklariert. Der Datentyp ist identisch mit dem vorher verwendeten Signal Qi. Damit der Prozess einen Wert von Vi nach außen kommunizierten kann, wird als Signal Qi ein einzelnes Bit beibehalten. Diesem Signal übergibt das Prozess process (Clk) dann ein Bit der Variablen Vi. Um Variablen und Signale besser auseinander halten zu können, ist die Syntax bei der Wertübergabe unterschiedlich (":=" bei Variablen, siehe Programmtext).

```

--- Demonstrate Signals and Variables (VHDL)

library ieee;

use ieee.std logic 1164.all;

entity SigVarDemo is

port ( Clk : in std logic; -- clock

D : in std logic; -- one bit in

Q : out std logic); -- one bit out

end SigVarDemo;

architecture RTL of SigVarDemo is

signal Qi: std logic := '0'; -- one bit internal signal

begin

-- first process using Vi and Qi

process (Clk)

variable Vi: std logic vector (2 downto 0) := (others =>'0');

begin

if rising edge(Clk) then

-- Version 1:

-- Version 2:

Vi(2) := Vi(1);

-- Vi(0) := D;

Vi(1) := Vi(0);

-- Vi(1) := Vi(0);

Vi(0) := D;

-- Vi(2) := Vi(1);

end if;

Qi \leftarrow Vi(2);

end process;

Q <= Qi;

-- second process using Qi

end RTL;

```

Übung 2.5: Testen Sie beide Programmversionen, die Variablen benutzen mit Hilfe des Testprogramms aus Übung 1.7. Hinweis: Die zweite Variante findet sich als Kommentar im Programmtext oben. Entsprechen die Ergebnisse Ihren Erwartungen? Erklären Sie das Verhalten der Schaltungen in beiden Fällen. Welche Unterschiede ergeben sich bzgl. der Verwendung von Signalen und Variablen durch Prozesse?

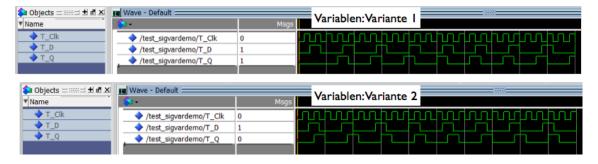

Die Testläufe beider Varianten zeigen folgende Ergebnisse (das Testprogramm schreibt wiederum ein Muster 010 010 ... auf den Eingang des Prüflings):

Bild 2.2 Testläufe beider Varianten

Hier ergeben sich gravierende Unterschiede: Variante 1 verhält sich wie ein 3-Bit Schieberegister, Variante 2 wie ein D-Flip-Flop (einfache Abtastung mit steigender Taktflanke). Der Vollständigkeit halber folgt an dieser Stelle noch das verwendete Testprogramm.

```

--- Test SigVarDemo (VHDL)

library ieee;

use ieee.std logic 1164.all;

entity Test SigVarDemo is

end Test SigVarDemo;

architecture Behavioural of Test SigVarDemo is

component SigVarDemo is

port ( Clk : in std logic; -- clock

D : in std_logic; -- one bit in

Q : out std logic); -- one bit out

end component;

-- testbench internal signals

signal T Clk: std logic;

signal T_D : std_logic := '0';

signal T Q : std logic;

begin

-- connect DUT to testbench

DUT: SigVarDemo port map (Clk => T Clk, D => T D, Q => T Q);

-- run tests

count: process -- write 010 010 ... pattern to D

begin

T D <= '0';

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

T D <= '1';

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

```

```

T_D <= '0';

T_Clk <= '0'; wait for 10 ns; T_Clk <= '1'; wait for 10 ns;

end process count;

end Behavioural;</pre>

```

#### 2.2. FIR Filter

Die Faltung einer zeitdiskreter Funktionen x(i) mit der Impulsantwort  $h_k$  wird durch die Faltungssumme

$$y[n] = \sum_{k} h_k \cdot x[n-k] \tag{2.1}$$

beschrieben, wobei der Index k über alle vorhandenen Stützstellen  $h_k$  verläuft. Für eine Impulsantwort mit insgesamt 5 Stützstellen ergibt sich folgende Gleichung.

$$y[n] = h_0 \cdot x[n] + h_1 \cdot x[n-1] + h_2 \cdot x[n-2] + h_3 \cdot x[n-3] + h_4 \cdot x[n-4]$$

(2.2)

Bei der Realisierung werden wiederholte Multiplikationen und Additionen erforderlich. Wegen der Möglichkeit zur Parallelverarbeitung und der Realisierbarkeit individuell zugeschnittener Rechenwerke eignen sich der HDL-Entwurf für Filter zur Signalverarbeitung.

Übung 2.6: Geben Sie als Eingangssignal einen Impuls vor, d.h. x(0) = 1 und x(n) = 0 für  $n \neq 0$ . Berechnen Sie mit Hilfe von Gleichung (2.2) die Impulsantwort y(n).

Übung 2.7: Geben Sie als Eingangssignal eine Sprungfunktion vor, d.h. x(n) = 1 für  $n \ge 0$  und x(n) = 0 für n < 0. Berechnen Sie mit Hilfe von Gleichung (2.2) die Sprungantwort y(n).

Bei der Realisierung von Filtern bedeuten die Stützstellen  $h_k$  die Filterkoeffizienten. Da direkt nach Gleichung (3.2) implementierte Filter stets eine endliche Anzahl von Filterkoeffizienten haben, ist auch die Impulsantwort endlich. Solche Filter werden als FIR-Filter bezeichnet, wobei FIR auf die endliche Impulsantwort hinweist (Finite Impulse Response).

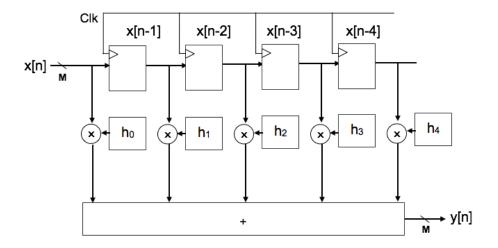

#### Rechenwerk für FIR Filter

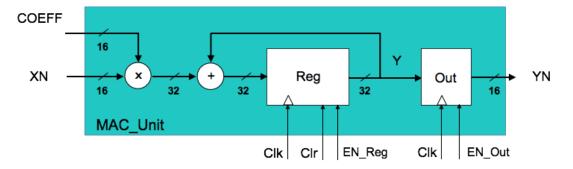

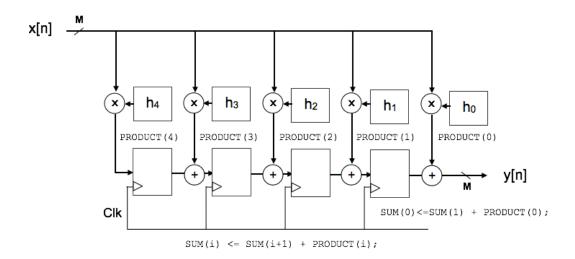

Für die in Gleichung (3.2) wiederholt auftretenden Additionen und Multiplikationen lässt sich ein spezielles Rechenwerk verwenden, wie in folgender Abbildung gezeigt.

Bild 2.3 Rechenwerk für kumulierte Multiplikationen

Ein Filterkoeffizient  $h_k$  st in der Abbildung als COEFF bezeichnet, ein Eingangswert x(n) mit XN, sowie ein berechneter Ausgangswert y(n) bzw. ein Zwischenergebnis mit YN. Mit Hilfe der Signale EN\_Reg und EN\_Out lässt sich das Rechenwerk steuern. EN\_Reg aktiviert das Register Reg, das in diesem Fall als Akkumulator arbeitet: Mit jedem Takt wird eine Multiplikation ausgeführt und das Ergebnis auf das vorher berechnete Ergebnis addiert. Es ergibt sich pro Takt somit  $y[n] = h_k \cdot x[n-k] + y[n-1]$ . Hierbei sind die Eingangswerte x[n-k] mit den passenden Koeffizienten  $h_k$  durch ein geeignetes Steuerwerk bereit zu stellen. Eine Implementierung des speziellen Rechenwerks zeigt folgender HDL-Text.

```

--- MAC Unit for FIR Filters (VHDL)

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

entity MAC Unit is

port (Clk, Clr : in std_logic; -- clock, Clear MAC register EN_Reg : in std_logic; -- Enable MAC register EN_Out : in std_logic; -- Enable output register

XN : in std logic vector (15 downto 0);     -- input sample

COEFF : in std logic vector (15 downto 0); -- filter coeff.

YN : out std logic vector (15 downto 0)); -- output sample

end MAC Unit;

architecture RTL of MAC Unit is

signal Y : signed (31 downto 0); -- intermediate results

begin

MAC : process (Clk) -- perform Multiply-ACcumulate operation

begin

if rising edge(Clk) then

if (Clr = '1') then Y \le (others => '0'); -- clear MAC

elsif (EN Reg = '1') then

Y <= Y + signed(COEFF) * signed(XN);

end if;

end if;

end process MAC;

Sample Out: process (Clk) -- transfer result to output register

begin

if rising edge(Clk) and (EN Out = '1') then

YN <= std_logic_vector(Y(31 downto 16));

end if;

end process Sample Out;

end RTL;

```

Übung 2.8: Erläutern Sie Funktionen der beiden Prozesse des Rechenwerkes (inklusive der Steuersignale EN\_Reg und EN\_Out).

Übung 2.9: Skizzieren Sie einen Ablauf (identisch mit den Prozessen eines Testprogramms), mit dem sich das Rechenwerk verwenden lässt, um eine Impulsantwort zu berechnen.

Übung 2.10: Skizzieren Sie einen Ablauf (identisch mit den Prozessen eines Testprogramms), mit dem sich das Rechenwerk verwenden lässt, um eine Sprungantwort zu berechnen.

#### Festkomma-Arithmetik

Das im obigen HDL-Text beschriebene Rechenwerk arbeitet mit dem Datentyp signed, das als vorzeichenbehaftete ganze Zahl mit einer vorgegebenen Anzahl Bits interpretiert wird. Dieser Datentyp ist zusammen mit arithmetischen Operationen in der Bibliothek IEEE.numeric\_std.all definiert. Rechenoperationen im Festkommaformat sind hiermit sehr einfach zu beschreiben, wie das beschriebene Rechenwerk zeigt (siehe Multiplikationen und Additionen).

Hierbei ist zu beachten, dass sich bei der Addition zweier Zahlen das Ergebnis verdoppeln kann. Das Ergebnis der Addition zweier Zahlen benötigt also in aller Regel ein weiteres Bit. Bei der Multiplikation zweier Zahlen verdoppelt sich die Zahl der benötigten Bits. Diese Regeln folgen im binären Zahlensystem der geläufigen Arithmetik im dezimalen Zahlensystem.

Die arithmetischen Operationen wie Addition bzw. Multiplikation sind übrigens nicht auf ganze Zahlen beschränkt, sondern gelten generell für Zahlen mit einem fest definierten Dezimalpunkt bzw. Komma, den sogenannten Festkommazahlen. Das Komma (bzw. der Dezimalpunkt im 10-er System) ist hierbei eine reine Frage der Interpretation und hat keinerlei Auswirkung auf die Rechenoperationen bzw. Rechenwerke. Ob man im dezimalen System eine Zahl "200" als "200,", "20,0", "2,00" bzw. als "0,200" interpretiert, ist nur eine Vereinbarung.

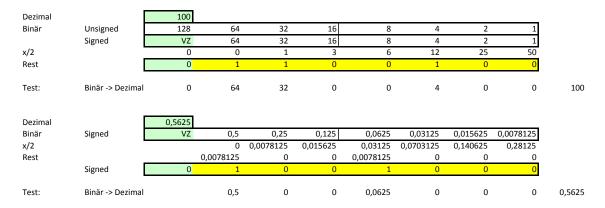

Die gleiche Interpretation gilt im binären Zahlenformat, wobei hierbei allerdings die dezimalen Zahlen in binäre Zahlen umzuwandeln sind. Durch fortgesetzte Division durch 2 und Mitschreiben des jeweiligen Rests (0 oder 1) erhält man aus 100 beispielsweise die binäre Zahl 0110 0100. Die folgende Abbildung zeigt das Rechenschema (beginnend mit der kleinsten binären Stelle). Je nach Datentyp, wird das höchstwertige Bit (MSB) entweder als Zahl (Datentyp Unsigned) oder als Vorzeichen (Datentyp Signed) interpretiert.

Bild 2.4 Umwandlung dezimal nach binär

Die Interpretation des Festkommas ist von dieser Darstellung unabhängig: In der Abbildung oben wurde die kleinste binäre Stelle als 1 interpretiert, das Komma steht somit rechts von der kleinsten Stelle. Stellt man das Komma vor die binäre Zahl, wäre die kleinste binäre Stelle als 1/128

zu interpretieren. In dieser Darstellung sind dann Zahlen darstellbar, deren Betrag kleiner als 1 ist. Die dezimale Zahl 0,5625 wird bei dieser Sichtweise in die binäre Zahl 0100 1000 gewandelt. Die Wandlung zurück ins dezimale Format erhält man wiederum als 1\* 64/128 + 1\* 8/128 = 72/128 = 0,5625.

Das Festkomma gilt als Vereinbarung, wie die dezimalen bzw. binären Stellen einer Zahl zu interpretieren sind. In die binäre Kodierung der Zahl muss diese Vereinbarung nicht übernommen werden, hierfür ist also kein eigenes Bit erforderlich. Allerdings erfordert das Vorzeichen beim Datentyp signed ein eigenes Vorzeichenbit (erstes Bit, MSB). Die Darstellung vorzeichenbehafteter binärer Zahlen folgt dem Zweierkomplement.

Übung 2.11: Erstellen Sie mit Hilfe Ihres Programms zur Tabellenkalkulation eine Tabelle zur Umrechnung dezimaler Festkommazahlen in binäre 16-Bit Festkommazahlen vom Typ. Das Komma soll hierbei unmittelbar auf das Vorzeichen der 16-Bit Zahl folgen. Wandeln Sie zum Test die Zahl 0,5625 in das 16-Bit Format. Hinweis: Verwenden Sie die Funktion Rest zur Berechnung des Restes der Division. Verwenden Sie zunächst nur positive Zahlen.

# Berechnung der Filterkoeffizienten

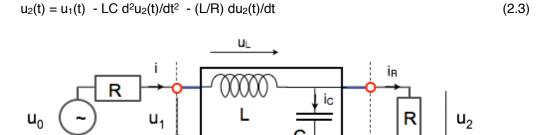

In vorliegenden Manuskript stehen Rechenwerke in HDL im Vordergrund. Die Berechnung von Filterkoeffizienten ist Teil der Theorie zeitdiskreter Systeme. An dieser Stelle erfolgt daher nur eine Plausibilisierung der Filterkoeffizienten durch den Vergleich mit einem realen System. Als Beispiel wird hierfür ein mit diskreten Bauteilen aufgebautes LC-Filter untersucht, wie in folgender Abbildung dargestellt.

Hierbei lässt sich die Ausgangsspannung  $u_2(t)$  in Abhängigkeit der Eingangsspannung  $u_1(t)$  in Form einer Differentialgleichung wie folgt beschreiben.

Bild 2.5 LC-Filter

Übung 2.12: Leiten Sie die Differentialgleichung (2.3) her. Hinweis: Verwenden Sie hierzu die Beziehungen  $u_L(t) = L di(t)/dt$  und  $i_C(t) = C du_2(t)/dt$ .

Gleichung (2.3) lässt sich so interpretieren, dass die Ausgangsspannung  $u_2(t)$  der eingeprägten Eingangsspannung  $u_1(t)$  folgt, bis auf die Ausdrücke mit den Ableitungen von  $u_2(t)$ . Da die Ableitungen nur auf Veränderungen reagieren, klingen diese Beiträge bei einer konstant verlaufenden Eingangssignal ab. Gibt man als Eingangsspannung  $u_1(t)$  beispielsweise eine Sprungfunktion vor  $(u_1(t) = \hat{u})$  für t

$\geq 0$  und  $u_1(t) = 0$  für n < 0), so wird sich das Ausgangssignal  $u_2(t)$  nach Abklingen der transienten Beiträge ebenfalls auf den konstanten Wert û einschwingen.

Der transiente Anteil des Ausgangssignals folgt hierbei einer gedämpften Schwingung. Für  $u_1(t)$  = 0 beschreibt die Differentialgleichung (2.3) einen gedämpften Schwingkreis und entspricht der folgender allgemeinen Form.

$$\ddot{y}(t) + 2\delta \dot{y}(t) + \omega_{o^2} y(t) = 0 \tag{2.4}$$

Die Konstante  $\delta$  wird hierbei als Abklingkoeffizient bezeichnet. Mit  $\omega_0$  ist die Eigenfrequenz des ungedämpften Schwingkreises bezeichnet. Beide Parameter lassen sich aus den Werten von R, L, und C berechnen. Die Gleichung der gedämpften Schwingung gemäß (2.4) wird durch Funktionen folgenden Typs gelöst:

$$y(t) = \hat{y}_0 e^{-\alpha t} \sin(\phi) = \hat{y}_0 e^{-\alpha t} \sin(\omega_0 t + \phi_0)$$

(2.5)

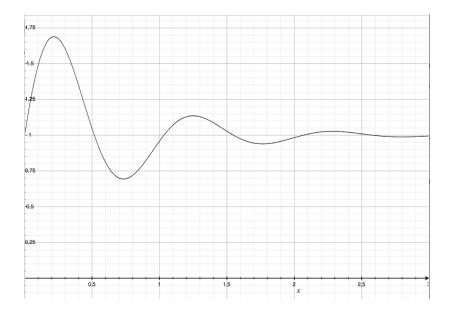

Zusätzlich zum periodischen Anteil  $sin(\varphi)$  enthält diese Funktion einen mit der Zeit exponentiell abklingenden Anteil  $e^{.\delta t}$ . Die Frequenz der Schwingung ist ebenfalls gedämpft. Die Kreisfrequenz der gedämpften Schwingung in Gleichung (2.5) mit  $\omega_d$  bezeichnet (Eigenfrequenz der gedämpften Schwingung). Der gedämpfte Schwingkreis schwingt mit der Frequenz  $\omega_{d^2} = \omega_{0^2}$  -  $\delta^2$  Die Dauer einer Periode beträgt folglich  $T_d = 2\pi / \omega_d = 2\pi / \sqrt{(\omega_{0^2} - \delta^2)}$ . Die Sprungantwort hat daher qualitativ den in folgender Abbildung gezeigten Verlauf.

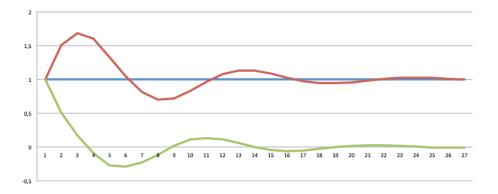

Bild 2.5 Sprungantwort des LC-Filters

Bei einem zeitdiskreten System erhält man die Eingangssignale und Ausgangssignale durch Abtastung mit einem festen Zeitintervall. Diskretisiert man den oben gezeigten qualitativen Verlauf der Sprungantwort, so ergeben sich die in folgender Abbildung gezeigten Werte. Hierbei wurde das Abtastintervall völlig willkürlich gewählt. Die obere Kurve entspricht der Sprungantwort.

S. Rupp, 2015

Bild 2.6 Sprungantwort und Impulsantwort des zeitdiskreten Systems

Aus der Sprungantwort lässt sich in einem zeitdiskreten System mit geringem Aufwand die Impulsantwort rekonstruieren. Mit Blick auf die Gleichungen (2.1) und (2.2), sowie die Übungen 2.6 und 2.7 erkennt man folgenden Zusammenhang:  $y_{Imp}(i) = y_{Sprung}(i) - y_{Sprung}(i-1)$ . Die Impulsantwort ist in der unteren Kurve in der Abbildung gezeigt.

Die Stützstellen der Impulsantwort entsprechen den Filterkoeffizienten eines FIR-Filters. Mit Hilfe der Faltungssumme lässt sich aus diesen Filterkoeffizienten die Reaktion des Systems auf beliebige Eingangssignale berechnen. Bei einem System, das das Eingangssignal nicht verstärkt, ist die Summe aller Filterkoeffizienten = 1 (bzw. der Betrag der Summe). Auch dieses Verhalten zeigt das oben genannte Beispiel: Da sich die Sprungantwort auf den Wert 1 einschwingt, addieren sich die Filterkoeffizienten zu diesem Wert.

#### Ein praktisches Beispiel

Mit Hilfe der im vorausgegangenen Abschnitt gezeigten Filterkoeffizienten soll mit Hilfe des eingangs beschriebenen Rechenwerkes die Sprungantwort des Systems berechnet werden. Für die Sprungantwort ist ab der ersten Stützstelle das Eingangssignal konstant (=1). Daher müssen dem Rechenwerk nur noch die Filterkoeffizienten zugeführt werden. Durch das Steuersignal EN\_Reg kumuliert das Rechenwerk die Ergebnisse selbsttätig gemäß dem Verlauf der Sprungantwort (siehe Übung 2.7). Folgender Programmtext zeigt den grundsätzlichen Ablauf.

```

-- run tests

MAC : process -- calculate sample MAC

begin

-- clear MAC

T Clr <= '1';

T Clk \leq ,0'; wait for 10 ns; T Clk \leq '1'; wait for 10 ns;

T Clr <= '0';

T Clk \leftarrow ,0'; wait for 10 ns; T Clk \leftarrow '1'; wait for 10 ns;

-- operate MAC for sample signal (step response)

T EN Reg <= '1';

-- Enable MAC

T EN Out <= '1';

-- Enable Output register

T XN <= "0111 1111 1111 1111"; -- set input to 1 for step response

T COEFF <= "0111 1111 1111 1111";

-- h0 (one clock cycle)

```

Zur Berechnung der Filterkoeffizienten wird folgende Tabelle verwendet. Die Umrechnung der im dezimalen Format gegebenen Filterkoeffizienten in das binäre Format mit Vorzeichen für den Datentyp signed erfolgt mit der im vorausgegangenen Abschnitt beschriebenen Methode (siehe Übung 2.11). Hierbei kann man sich mit guter Näherung auf die ersten 13 Stützstellen beschränken (mit Index 0 bis 12).

| Sprungantwort und Impulsantwort Index Sprungfkt Sprungantwort Impulsantwort Binärformat |           |               |               |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|-----------------------------------------------------------------------------------------|-----------|---------------|---------------|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| inaex                                                                                   | Sprungtkt | Sprungantwort | Impulsantwort |    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

|                                                                                         |           |               |               | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| 0                                                                                       | 1         | 1             | 1             | 0  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1                                                                                       | 1         | 1,508         | 0,508         | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| 2                                                                                       | 1         | 1,685         | 0,177         | 0  | 0  | 0  | 1  | 0  | 1  | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| 3                                                                                       | 1         | 1,599         | -0,086        | 1  | 1  | 1  | 1  | 0  | 1  | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 4                                                                                       | 1         | 1,331         | -0,268        | 1  | 1  | 0  | 1  | 1  | 1  | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 5                                                                                       | 1         | 1,042         | -0,289        | 1  | 1  | 0  | 1  | 1  | 0  | 1 | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 6                                                                                       | 1         | 0,813         | -0,229        | 1  | 1  | 1  | 0  | 0  | 0  | 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 |

| 7                                                                                       | 1         | 0,7           | -0,113        | 1  | 1  | 1  | 1  | 0  | 0  | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| 8                                                                                       | 1         | 0,72          | 0,02          | 0  | 0  | 0  | 0  | 0  | 0  | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 1 |

| 9                                                                                       | 1         | 0,829         | 0,109         | 0  | 0  | 0  | 0  | 1  | 1  | 0 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 1 | 1 |

| 10                                                                                      | 1         | 0,963         | 0,134         | 0  | 0  | 0  | 1  | 0  | 0  | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 1 | 1 |

| 11                                                                                      | 1         | 1,073         | 0,11          | 0  | 0  | 0  | 0  | 1  | 1  | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| 12                                                                                      | 1         | 1,131         | 0,058         | 0  | 0  | 0  | 0  | 0  | 1  | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 13                                                                                      | 1         | 1,129         | -0,002        | 1  | 1  | 1  | 1  | 1  | 1  | 1 | 1 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 1 |

Bild 2.7 Stützstellen der Impulsantwort als Filterkoeffizienten

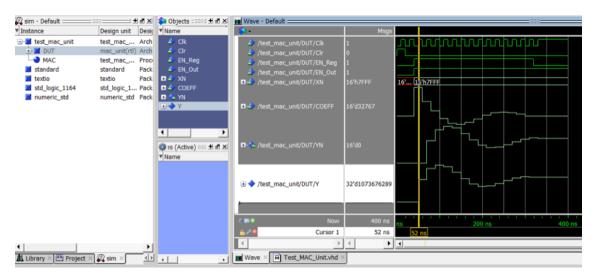

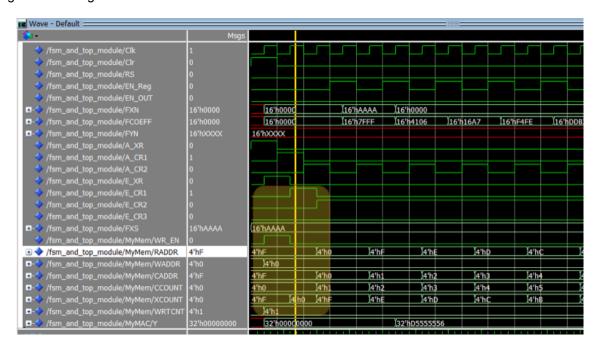

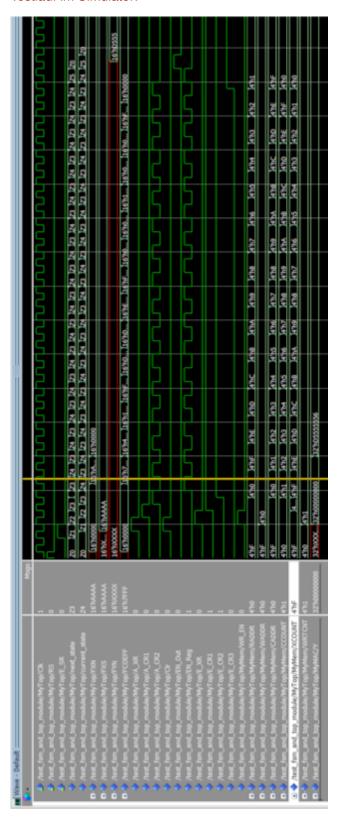

Ein Testlauf des Programms die Sprungantwort an den Zwischenergebnissen im Zeitdiagramm anschauen lässt, siehe folgende Abbildung. Das Eingangssignal verbleibt als Sprungfunktion auf konstanten Niveau. Da zuvor alle internen Register gelöscht wurden, startet die Berechnung ab der ersten Stützstelle der Eingangsfunktion. Die durch das Testprogramm jeweils vorgegebenen Filterkoeffizienten entsprechen hierbei in Ihrer Reihenfolge der Impulsantwort des Systems.

Mit der Vorgabe EN\_Reg kumuliert das Rechenwerk die Stützstellen wieder zur Sprungfunktion, was der Verlauf des Signals im internen Register Y in der Abbildung ganz unten zeigt. Die Ausgabe auf das Ausgangssignal YN wird durch das Steuersignal EN\_Out vorgegeben und erfolgt einen Takt später.

Bild 2.8 Berechnung der Sprungantwort mit Hilfe des Testprogramms

Übung 2.13: Erstellen Sie ein Testprogramm für das Rechenwerk, das die Sprungantwort mit den im oben genannten Beispiel gegebenen Filterkoeffizienten mit 12-Bit Wortbreite für die Sprungfunktion und die Filterkoeffizienten berechnet. Testen Sie das Programm am Simulator.

Übung 2.14: Erstellen Sie mit Hilfe des Testprogramms ein Filter, das mehrere Stützstellen des Eingangssignals mittelt, das also eine Impulsantwort in Form eines Rechtecks hat. Durch diese Mittelung ergibt sich ebenfalls eine Tiefpasswirkung. Wählen Sie für das Filter beispielsweise 5 Stützstellen und skalieren Sie die Filterkoeffizienten so, dass sich die Sprungantwort auf die Höhe des Eingangssignals einschwingt (Verstärkung = 1). Berechnen Sie die Sprungantwort.

## FIR Filter als Systemmodell

FIR bilden das Verhalten eines Systems durch Reproduktion der Impulsantwort nach. Im Vergleich zum realen physikalischen System, wie der in der vorausgegangenen Abschnitten gezeigten LC-Schaltung, erschient die Nachbildung jedoch wenig effizient. Für die Beschreibung des realen Systems genügen sehr wenige Parameter, nämlich die Werte von R, L und C. Im Vergleich hierzu benötigt das FIR-Filter selbst für eine recht grobe Näherung bereits mehr als 12 Systemparameter (Filterkoeffizienten).

Die Ursache hierfür liegt darin, dass mit Hilfe der Differentialgleichung (2.3) beschriebene reale System Rückkopplungen verwendet. Der FIR-Algorithmus gemäß Gleichung (2.1) bzw. Gleichung (2.2) berechnet die Stützstellen des Ausgangssignals jedoch ausschließlich aus den Stützstellen des Eingangssignals mit Hilfe der Filterkoeffizienten. Somit ist für jede Stützstelle der Impulsantwort ein Filterkoeffizient erforderlich. Mit einem Filteralgorithmus folgender Form ließe sich die Zahl der erforderlichen Parameter zur Nachbildung des Systems deutlich reduzieren.

$$y[n] = \sum a_k \cdot x[n-k] - \sum b_l \cdot y[n-l]$$

(2.6)

S. Rupp, 2015 T2ELN3804 , T2ELA3004.1 28/134

Während der erste Teil mit den Koeffizienten a<sub>k</sub> der Struktur des FIR-Filters, koppelt der zweite Teil des Algorithmus vergangene Werte des Ausgangssignals y[n–I] mit Hilfe der Koeffizienten b<sub>i</sub> zurück. Die Wirkungsweise der Gleichung verdeutlicht die folgende vereinfachte Form.

$$y[n] = a_0 \cdot x[n] - b_1 \cdot y[n-1]$$

(2.7)

Wählt man beispielsweise  $a_0 = 1$  und  $b_1 = 0.8$ , so klingt die Impulsantwort des Filters ohne Beschränkung sehr lange aus, unabhängig von der Anzahl der Filterkoeffizienten. Wegen der im Vergleich zum FIR-Filter unbegrenzten Dauer der Impulsantwort werden solche Algorithmen auch als IIR Filter bezeichnet (wobei IIR für Infinite Impulse Response steht).

Die Nachbildung von Systemen mit rückgekoppelten Algorithmen erfordert belastbare Kenntnisse der Systemtheorie, sowohl was die Modellierung betrifft, als auch die Stabilität der Modelle (um ein Aufschwingen zu verhindern). Weiterhin setzt auch die Implementierung der Algorithmen in Festkomma-Arithmetik belastbare Kenntnisse des numerischen Verhaltens voraus. Davon abgesehen stellt die Implementierung in HDL keine Anforderungen, die über die Implementierung der FIR-Algorithmen hinaus gehen.

#### 2.3. Steuerwerk für das FIR Filter

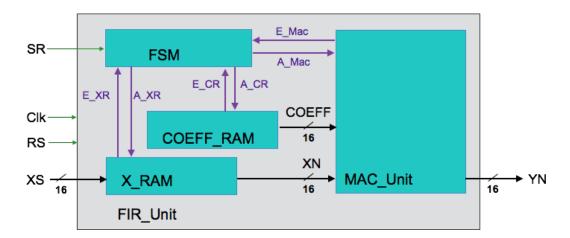

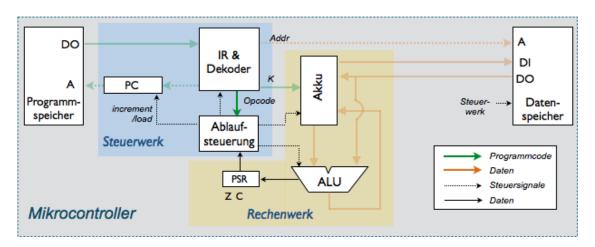

Das in Abschnitt 2.2 gezeigte Rechenwerk soll nun um ein geeignetes Steuerwerk erweitert werden. Hierbei sollen die Filterkoeffizienten innerhalb des Filters gespeichert werden. Von aussen werden die abgetasteten Eingangssignale zugeführt. Das Filter soll den Faltungsalgorithmus gemäß Gleichung (2.1) für alle vorhandenen Koeffizienten eigenständig durchführen. Der Ablauf wäre dann wie folgt: (1) den neuen Eingangswert x(n) einlesen, (2) die Faltungssumme ausführen, (3) den aktuellen Ausgangswert y(n) ausgeben.

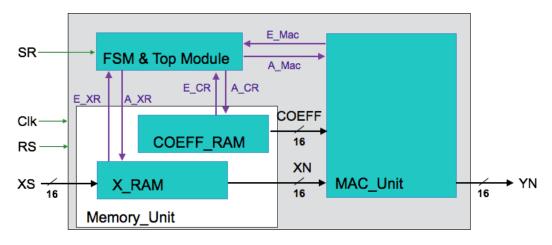

Da der Faltungsalgorithmus auch die vergangenen Eingangssignale für die gegebene Anzahl von Filterkoeffizienten benötigt, sind die eingelesenen Eingangssignale ebenfalls zu speichern. Demnach besitzt das FIR-Filter folgende Komponenten: (1) das Rechenwerk (MAC\_Unit), (2) einen Speicher für Koeffizienten (COEFF\_RAM), (3) einen Speicher für Eingangswerte (X\_RAM), (4) ein Steuerwerk (FSM). Folgendes Blockschaltbild zeigt einen Entwurf des Filters.

Bild 2.9 Blockschaltbild des Filters mit Rechenwerk und Steuerwerk

Dem Filter wird ein abgetasteter Wert des Eingangssignals XS zugeführt. Mit Hilfe der Koeffizienten berechnet das Filter hieraus den aktuellen Abtastwert des Ausgangssignals YN. Das

Steuersignal SR (Sample Ready) zeigt dem Filter an, dass ein neuer Abtastwert als Eingangssignal vorhanden ist. Ausserdem sind als Eingänge ein Takt (Clk), sowie ein Reset (RS) vorhanden. Die Weiterführung dieser Signale an die einzelnen Komponenten ist der Übersichtlichkeit halber nicht dargestellt.

Die Steuerung erfolgt durch einen Zustandsautomaten (FSM), der Eingänge und Ausgänge zu allen übrigen Komponenten besitzt. Diese Signale sind noch nicht näher spezifiziert, bis auf die bereits vorhandenen Steuersignale der MAC-Unit. Diese Steuersignale (EN\_Reg, EN\_Out und Clr) sind in der Abbildung unter dem Vektor A\_MAC zusammengefasst. Für den eingangs beschriebenen Ablauf sind innerhalb der einzelnen Komponenten Zähler vorzusehen, die ein taktsynchrones Arbeiten ermöglichen. Die Anzahl der Filterkoeffizienten wird hierfür fest vorgegeben, beispielsweise für 32 Koeffizienten. Hieraus folgt dann die Dimensionierung der Speicher und Zähler.

#### Aufbau der Speicher

Die Speicher werden als Arrays definiert, die das Synthesewerkzeug je nach der auf dem Zielbaustein vorhandenen Infrastruktur dann entweder in Tabellen (Look-up Tables) oder Speicherzellen (RAM) abbildet. Der grundsätzliche Aufbau wäre wie folgt. Der Speicher stellt ein Array von Worten dar. Da Arrays mit dem Datentyp Integer adressiert werden, ist für den Zugriff auf die gegebene Speicheradresse eine Typenkonversion von std\_logic\_vector nach Integer erforderlich.

```

--- RAM Module

library ieee;

use ieee.std logic 1164.all;

use IEEE.numeric std.all;

entity RAM is

generic (L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

port ( ADDR : in std logic vector(L BITS-1 downto 0);

DATA: out std logic vector(M BITS-1 downto 0));

end RAM;

architecture RTL of RAM is

-- array of 2**L samples, each M bits wide

type RAM array is array(0 to 2**L BITS - 1) of

std logic vector(M BITS - 1 downto 0);

-- fill array with 2**M sample values

signal memory: RAM array := (x"0." -- fill in values here);

-- read access: y = data(address)

DATA <= memory(to integer(unsigned(ADDR)));</pre>

```

```

end RTL;

```

Das Beispiel beschreibt einen Speicher, der statisch beschrieben und nur gelesen wird (also ein ROM, wie es für die Koeffizienten benötigt wird). Für ein RAM wäre eine Schreibfunktion zu ergänzen, d.h. die Zuweisung von Eingangsdaten an die Speicheradresse. Für ein Filter mit 16 Stützstellen wären L = 4 Adressleitungen ausreichend. Da die Wortbreite 16 Bit betragen soll, wäre M = 16. Diese Angaben gelten sowohl für den Koeffizientenspeicher als auch für den Speicher der Eingangswerte.

Folgende zusätzlichen Anforderungen bestehen: (1) Beide Speicher sollen takt-synchron arbeiten, d.h. die Ausgabe der Daten erfolgt einen Takt nach Vorgabe der Adressen, (2) der Koeffizientenspeicher soll zusätzlich einen Zähler erhalten, mit dem sich die Bereitstellung passender Paare von Koeffizienten und Eingangswerte herstellen lässt, (3) der Speicher für die Eingangssignale muss mit Null initialisieren lassen, (4) im Speicher für die Eingangs-signale werden Werte, die mehr als 32 Stützstellen in der Vergangenheit liegen, mit jeweils aktuellen Werten fortlaufend überschrieben.

# Aufbau des Speichers für die Eingangswerte

Der Speicher für die Eingangswerte soll als Dual-Ported RAM ausgeführt werden, d.h. mit separaten Adressen zum Lesen und zum Schreiben von Daten. Außerdem erhält der Speicher ein Steuersignal zum Schreiben (Write-Enable), das unnötige Schreiboperationen beim Auslesen des Speichers vermeiden soll.

```

--- X RAM Module (VHDL)

library ieee;

use ieee.std logic 1164.all;

use IEEE.numeric std.all;

entity X RAM is

generic (L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

port ( Clk, WR EN : in std logic; -- Clock, Write Enable

RADDR: in std logic vector(L BITS-1 downto 0);

DTOUT : out std logic vector(M BITS-1 downto 0);

WADDR: in std logic vector(L BITS-1 downto 0);

DATIN : in std logic vector(M_BITS-1 downto 0));

end X RAM;

architecture RTL of X RAM is

-- array of 2**L samples, each M bits wide

type RAM array is array(0 to 2**L BITS - 1) of

std logic vector(M BITS - 1 downto 0);

-- instantiate memory object of X RAM

signal memory : RAM array;

```

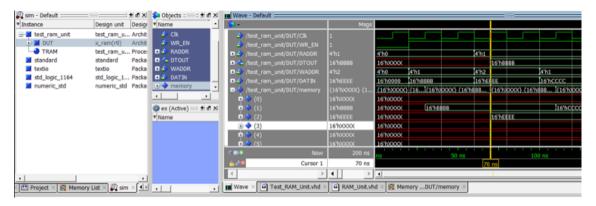

Je nach Vorgabe des Write\_Enable Signals (WR\_EN) führt der Speicher bei einer steigenden Taktflanke eine Schreiboperation und eine Leseoperation durch, bzw. nur eine Leseoperation. Beim Schreiben und Lesen auf die gleiche Adresse benötigt das Speicher zwei Taktflanken, da mit der ersten Taktflanke noch der alte Wert vorhanden ist, der zu diesem Zeitpunkt erst aktualisiert wird. Folgendes Testprogramm zeigt die Arbeitsweise des Speichermoduls.

```

--- Testbench für X RAM (test cases only)

-- write

T WR EN <= '1';

T WADDR <= x"1";

T DATIN <= x"BBBB";

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

-- write & read simultaneously at different addresses

T WR EN <= '1';

T WADDR <= x"2";

T DATIN <= x"EEEE";

T RADDR \leq x"1";

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

-- write & read simultaneously at the same address

T WR EN <= '1';

T WADDR <= x"1";

T DATIN <= x"CCCC";

T RADDR <= x"1";

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

T Clk <= '0'; wait for 10 ns; T Clk <= '1'; wait for 10 ns;

```

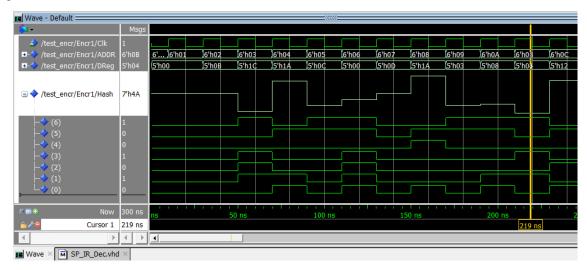

Das Zeitdiagramm zeigt, das simultanes Schreiben und Lesen an unterschiedlichen Adressen mit der nächsten steigenden Taktflanke erfolgt. Simultanes Schreiben und Lesen der gleichen Adresse benötigt erwartungsgemäß zwei Taktflanken.

Bild 2.10 Zeitverhalten des X\_RAM

## Aufbau des Speichers für Koeffizienten

Der Speicher für die Koeffizienten kann als reines ROM ausgeführt werden. Wenn die Koeffizienten fest vorgegeben werden können, kann die Vorgabe direkt im Programmtext erfolgen, wie in folgenden HDL-Text beschrieben.

```

--- COEFF ROM Module (VHDL)

library ieee;

use ieee.std logic 1164.all;

use IEEE.numeric std.all;

entity COEFF ROM is

generic (L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

port ( Clk : in std_logic; -- Clock

CADDR : in std_logic_vector(L_BITS-1 downto 0);

CFOUT: out std logic vector (M BITS-1 downto 0));

end COEFF ROM;

architecture RTL of COEFF ROM is

-- array of 2**L samples, each M bits wide

type ROM array is array(0 to 2**L BITS - 1) of

std_logic_vector(M_BITS - 1 downto 0);

-- instantiate memory object of COEFF ROM

signal cmemory : ROM array := (

0 => "011111111111111", -- h0

1 => "0100000100000110",

```

```

2 => "0001011010100111", -- h2

3 => "11110100111111110", -- h3

4 => "1101110110110011", -- h4

5 => "1101101100110011", -- h5

6 => "1110001010110001", -- h6

7 => "1111000110001001", -- h7

8 => "0000001010001111", -- h8

9 => "0000110111110011", -- h9

10 => "0001000100100111", -- h10

11 => "0000111000010100", -- h11

12 => "0000011101101101", -- h12

13 => "111111111111111", -- h13

14 => "000000000000000", -- h14

15 => "000000000000000"); -- h15

begin

-- read process

process (Clk) begin

if (rising edge(Clk)) then

CFOUT <= cmemory(to integer(unsigned(CADDR)));</pre>

end if;

end process;

end RTL;

```

#### Zähler zur Berechnung der Faltungssumme

Es verbleibt noch die Steuerung der Adressen für die Koeffizienten und die passenden Stützstellen der Eingangsfunktion aus dem X\_RAM. Mit Blick auf die Faltungssumme gemäß Gleichung (2.1) bzw. (2.2) wird hierfür ein Zähler benötigt, der einerseits die Koeffizienten von Index 0 bis 15 adressiert, andererseits die Stützstellen beginnend vom aktuellen Eingangswert x(n) abwärts bis x(n-15) adressiert. Diese Aufgabe kann durch folgende Beschreibung gelöst werden.

Für 16 Koeffizienten sind beide Zähler 4-Bit-Zähler mit automatischem Überlauf bzw. Unterlauf. Der Zähler für die Eingangswerte startet bei der letzten beschriebenen Speicheradresse, die den aktuellen Wert von x(n) enthält und zählt von dort aus abwärts. Da das X-RAM ebenfalls als

Ringpuffer organisiert ist, erreicht dieser Zähler von der aktuellen Stützstelle aus die vergangenen 15 Werte. In diesem Fall bietet es sich an, die beiden Speicher einem Modul unterzuordnen, das die Zähler enthält und die Durchführung einer Faltungssumme eigenständig übernimmt.

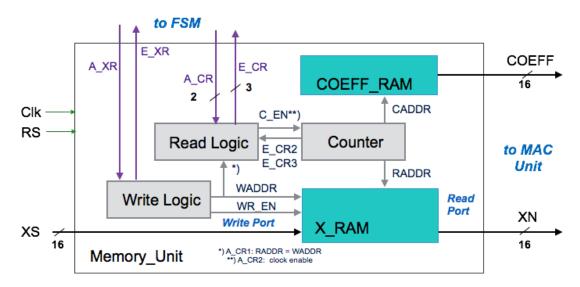

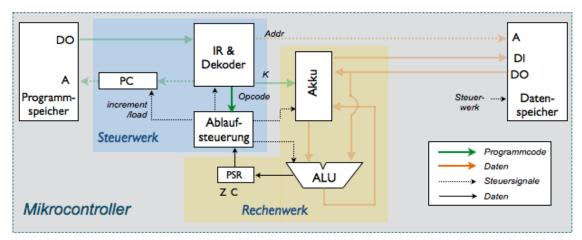

Die Speicher mit den Zählern und ihrer Steuerlogik werden im folgenden zu einem Modul zusammengefasst (Memory-Unit), wie in der folgenden Abbildung gezeigt. Hierbei übernimmt eine Steuerlogik im Datenpfad die Aufgabe, das Schreiben und Lesen der beiden Speicher zu organisieren und zum Zustandsautomaten zu kommunizieren. Der Zustandsautomat steuert bei dieser Vorgabe jede einzelne Transaktion zum Lesen beider Speicher, bzw. zum Schreiben des Speichers für die Eingangswerte.

Bild 2.11 Steuerung im Datenpfad

Die Memory-Einheit führt auf Anweisung des Zustandsautomaten folgende Operationen aus:

- (1) Schreiben eines neuen Eingangswertes in das XRAM an die Adresse WADDR. Diese Adresse wird von der Lese-Logik als Startpunkt für das erste Faltungsprodukt h<sub>0</sub> \* x(n) verwendet. Für den nächsten Eingangswert Wert wird die Adresse inkrementiert. Zum Schreiben wird das Write-Enable Signal des X\_RAMs verwendet. Die Schreiboperation wird vom Zustandsautomaten mit dem Signal A\_XR ausgelöst und die Ausführung vom Datenpfad mit E XR quittiert.

- (2) Durchführung der Faltungssumme durch die Memory-Einheit und MAC-Einheit: Der Zustands-automat steuert jeden einzelnen Schritt über seine Eingänge und Ausgänge. Für jeden Koeffizienten wird folgende Transaktion ausgeführt:

- Synchronisation der Adresse (RADDR) zum Auslesen des ersten Wertes x(n) mit der zuletzt beschriebenen Speicheradresse (WADDR). Die Synchronisation wird mit dem Signal A\_CR1 ausgelöst und mit E\_CR1 quittiert.

- Auslesen eines Paares hi und x(n-i) aus der Memory-Unit. Hierfür wird als Clock-Enable-Signal (C\_EN) die Steueranweisung A\_CR2 verwendet, mit E\_CR2 als Quittung.

- Multiplikation der bereitgestellten Werte und Akkumulation der Ergebnisse in der MAC-Einheit.

- Die Bereitstellung des letzten Wertepaares signalisiert die Memory-Einheit mit Hilfe ihres Zählerstandes durch das Signal E\_CR3.

- (3) Ausgabe des Ergebnisses in der MAC-Einheit.

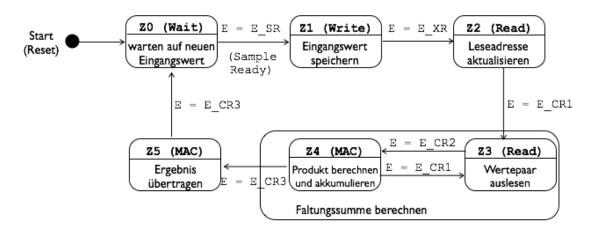

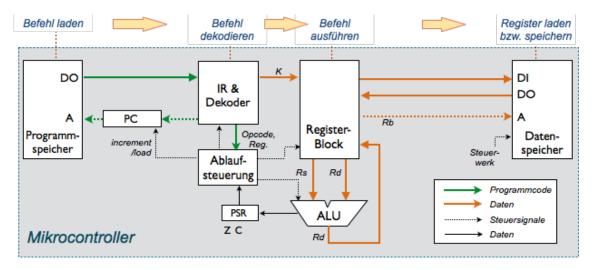

#### Entwurf des Zustandsautomaten

Mit der oben beschriebenen Abfolge ergibt sich für den Zustandsautomaten folgendes Diagramm. Initialzustand ist das Warten auf den ersten neuen Eingangswert. Die Ankunft eines neuen Wertes wird durch das Ereignis E= E\_SR (Sample Ready) gemeldet. Daraufhin wechselt der Automat in den Zustand Z1 und veranlasst das Speichern des Wertes mit Hilfe der Anweisung A\_XR. Die Quittung E\_XR führt den Automaten in den nächsten Zustand Z2, in dem er die Leseadresse für dien aktuellen Wert im X\_RAM aktualisiert. Hierfür wird gemäß der letzten Abbildung Die Anweisung A\_CR1 verwendet.

Bild 2.12 Zustandsdiagramm des Automaten

Der Automat steuert darauf den Speicher und das Rechenwerk mit Hilfe von Clock-Enable Signalen, d.h. durch Anschluss der Module an die Taktversorgung und Trennung der Module von der Taktversorgung. Eine besondere Herausforderung ist hierbei die zeitliche Synchronisation. Die Zustände während der Berechnung der Faltungssumme müssen im Taktzyklus wechseln, wo bei jeweils abwechselnd die Speichereinheit und die MAC-Einheit getaktet werden.

Das Ende der Faltungskette signalisiert das Zählwerk der Speichereinheit mit dem Signal E\_CR3, das gesetzt wird, sobald der letzte Koeffizient ausgelesen wurde. Nach einer finalen MAC-Operation wechselt der Automat dann in den Zustand Z5, in dem er die MAC-Einheit anweist, das Ergebnis aus dem internen Register auf den Ausgang zu schreiben. Nach der Ausgabe schaltet der wieder Automat in den Wartezustand.

#### Aufbau der Memory-Unit

Folgender HDL-Text beschreibt die Memory-Einheit. Der Aufbau deklariert die beiden Speicher X\_RAM und Koeffizienten-RAM als Komponenten und bindet diese ein. Die Funktion der Schaltung findet sich dann ein den beiden Prozessen counters und write\_logic.

```

--- Memory_Unit (VHDL)

library ieee;

use ieee.std_logic_1164.all;

use IEEE.numeric_std.all;

entity Memory_Unit is

```

```

-- define constants

generic ( L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

-- ports

port (Clk, RS : in std logic; -- Clock, Reset

A XR, A CR1, A CR2 : in std logic;

-- controls from FSM

E_XR, E_CR1, E_CR2, E_CR3 : out std_logic := '0'; -- events to FSM

MCOEFF, MXN : out std logic vector(M BITS - 1 downto 0); -- MAC

XS : in std logic vector(M BITS - 1 downto 0)); -- sample from ADC

end Memory Unit;

architecture RTL of Memory Unit is

component X RAM is

generic (L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

port (Clk, WR EN : in std logic; -- Clock, Write Enable

RADDR : in std logic vector(L BITS - 1 downto 0);

DTOUT : out std logic vector (M BITS - 1 downto 0);

WADDR: in std logic vector(L BITS - 1 downto 0);

DATIN : in std logic vector(M BITS - 1 downto 0));

end component;

component COEFF ROM is

generic (L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

port (Clk : in std logic; -- Clock, Write

CADDR : in std logic vector(L BITS-1 downto 0);

CFOUT : out std logic vector(M BITS-1 downto 0));

end component;

-- memory unit internal signals

signal WR EN : std logic := '0';

-- initialized with x"FF" in order to test synchonization

signal RADDR : std logic vector(L BITS-1 downto 0):= (others => '1');

signal WADDR : std logic vector(L BITS-1 downto 0):= (others => '1');

signal CADDR: std logic vector(L BITS-1 downto 0):= (others => '1');

signal CCOUNT : unsigned (L BITS-1 downto 0) := (others => '0');

signal XCOUNT : unsigned (L BITS-1 downto 0) := (others => '1');

signal WRTCNT : unsigned (L BITS-1 downto 0) := (others => '0');

begin

-- connect components

XR: X RAM generic map(L BITS => L BITS, M BITS => M BITS)

port map (Clk => Clk, WR EN => WR EN, RADDR => RADDR, DTOUT => MXN,

WADDR => WADDR, DATIN => XS);

CR: COEFF ROM generic map(L BITS => L BITS, M BITS => M BITS)

port map (Clk => Clk, CADDR => CADDR, CFOUT => MCOEFF);

```

```

-- run processes

counter: process (Clk, A CR1, A CR2) -- address counters & read logic

begin

if ((A CR1 = '1') \text{ and rising edge}(Clk)) then

XCOUNT <= unsigned(WADDR);</pre>

E CR1 <= '1';</pre>

end if;

if ((A CR2 = '1')) and rising edge(Clk)) then

CADDR <= std logic vector(CCOUNT);</pre>

RADDR <= std logic vector(XCOUNT);</pre>

CCOUNT <= CCOUNT + 1;

XCOUNT <= XCOUNT - 1;

if (CCOUNT = x"F") then E_CR3 <= '1';

else E CR3 <= '0';

end if;

E CR2 <= '1';</pre>

end if:

end process counter;

write logic : process(Clk, A XR) -- write logic (returns E XR)

begin

if rising edge (Clk) then

if (A XR = '1') then

WR EN <= '1';

WADDR <= std logic vector(WRTCNT);

WRTCNT <= WRTCNT + 1;

E XR <= '1';

else

WR EN <= '0';

E XR <= '0';

end if;

end if;

end process write logic;

end RTL;

```

Im Vergleich mit dem Blockschaltbild in Abbildung 2.11 umfasst der Prozess counters die beiden Blöcke Read-Logic und Counter. Dieser Prozess läuft parallel zum Prozess write\_logic, der den gleichnamigen Block in der Abbildung beschreibt. Der Zustandsautomat sollte zunächst mit Hilfe der Anweisung A\_XR mit der nächsten steigenden Taktflanke den Prozess write\_logic anstossen, der mit dem Clock Enable Signal WR\_EN des Schreibport des X\_RAMs aktiviert. Mit der nächsten Taktflanke wird der Wert dann abgespeichert. Der Prozess write\_logic inkrementiert die Schreibadresse für den nächsten Eingangswert und quittiert den Vorgang mit dem Signal E\_XR.

Der Prozess counter erfüllt folgende Aufgaben: (1) die Aktualisierung der Leseadresse für den Fall, dass ein neuer Eingangswert abgespeichert wurde, (2) das Bereitstellen der Adressen für ein Wertepaar (Eingangswert x(n-i) und Koeffizienten h<sub>i</sub>). Die Aktualisierung der Leseadresse erfolgt auf die Anweisung A\_CR1. Die Bereitstellung der Adressen erfolgt auf die Anweisung A\_CR2. Sobald alle Adressen der Koeffizienten durchgezählt wurden, wird die Meldung E\_CR3 abgesetzt, die das Ende der Faltungssumme für den gegebenen Eingangswert kennzeichnet.

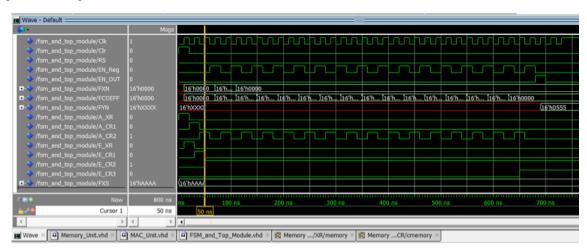

#### Test der Schaltung

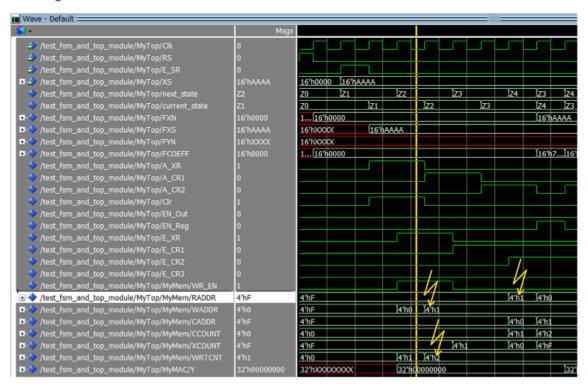

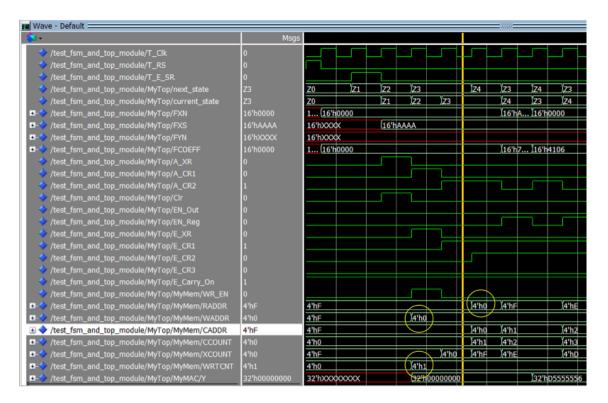

Bevor der Zustandsautomat weiter detailliert wird, erfolgt ein Test der Schaltung in einem Top-Modul, welches die Memory-Einheit und die MAC-Einheit enthält. Das Testprogramm verwendet alle Zustandsübergänge, bevor ein Automat eingesetzt wird. Diese Vorgehensweise arbeitet vom Groben ins Feine, indem erst einmal die Steuerung auf ihre Funktion überprüft wird. Folgender HDL-Text beschreibt das Top-Modul mit den Tests.

```

--- FSM and Top Module of FIR Filter (VHDL)

library ieee;

use ieee.std_logic_1164.all;

entity FSM and Top Module is

generic (L BITS : natural := 4;     -- L bits wide (Address Space)

M BITS : natural := 16); -- M bits wide (Word Width)

-- later: Clk, RS, SR, XS (sample in) as input ports,

-- YS (sample out) as output port

end FSM and Top Module ;

architecture RTL of FSM and Top Module is

component Memory_Unit is

generic (L BITS : natural; -- L bits wide (Address Space)

M BITS : natural); -- M bits wide (Word Width)

port ( Clk, RS : in std logic;

-- Clock, Reset

CIK, RS: in std_logic; -- Clock, Re

A_XR, A_CR1, A_CR2: in std_logic; -- from FSM

E XR, E CR1, E CR2, E_CR3 : out std_logic; -- to FSM

MCOEFF, MXN : out std logic vector(M BITS - 1 downto 0);

XS : in std logic vector(M BITS - 1 downto 0));

end component;

component MAC Unit is

EN Reg, EN Out : in std logic; -- Enable MAC register, output

XN : in std logic vector (15 downto 0); -- input sample

COEFF: in std_logic_vector (15 downto 0); -- filter coefficient

YN : out std logic vector (15 downto 0)); -- output sample

end component;

-- Top Module internal signals

signal FXN: std logic vector (15 downto 0); -- later: input port

signal FYN: std_logic_vector (15 downto 0); -- later: output port

signal SR : std logic := '0';

-- later: input port

signal Clr : std logic := '0';

signal EN Reg: std logic := '0';

```

```

signal EN OUT: std logic := '0';

signal FCOEFF: std logic vector (15 downto 0);

signal A_XR, A_CR1, A_CR2 : std_logic := '0'; -- control inputs of FSM

signal E XR, E CR1, E CR2, E CR3 : std logic; -- control events to FSM

signal FXS: std logic vector(M BITS - 1 downto 0); -- sample from ADC

begin

-- connect Memory Unit and MAC Unit to Top Module

MyMem: Memory Unit generic map(L BITS => L BITS, M BITS => M BITS)

port map (Clk=>Clk, RS=>RS, A XR => A XR, A CR1 => A CR1,

A CR2 \Rightarrow A CR2, E XR \Rightarrow E XR, E CR1\RightarrowE CR1, E CR2\RightarrowE CR2,

E CR3=>E CR3, MCOEFF=>FCOEFF, MXN=>FXN, XS=>FXS);

MyMAC: MAC Unit port map (Clk=>Clk, Clr=>Clr, EN Reg=>EN Reg,

EN Out=>EN Out, XN=>FXN, COEFF=>FCOEFF, YN=>FYN);

-- run processes

Test: process -- test MAC and Mem w/o FSM (each step one clock cycle)

begin

--- write sample value to memory

FXS <= x"AAAA";

A XR <= '1';

EN Out <= '0';

Clr <= '1'; -- clear MAC unit

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

-- synchronize XCOUNT/RADDR to WADDR (read from last write address)

if (E XR = '1') then

A XR <= '0';

A CR1 <= '1';

Clr <= '0'; -- deselect clear MAC unit

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

A CR1 <= '0';

-- start MAC operations

L1: for i in 1 to 16 loop

A CR2 <= '1';

EN Reg <= '0';

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

if (E CR2 = '1') then A CR2 <= '0'; end if;

EN Reg <= '1';

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

end loop L1;

-- copy result to MAC output register

if (E CR3 = '1') then

A_CR2 <= '0';

```

```

EN_Reg <= '0';

EN_Out <= '1';

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

EN_Out <= '0';

end if;

-- more clock cycles to check further acticities

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

Clk <= '0'; wait for 10 ns; Clk <= '1'; wait for 10 ns;

wait;

end process Test;

end RTL;</pre>

```

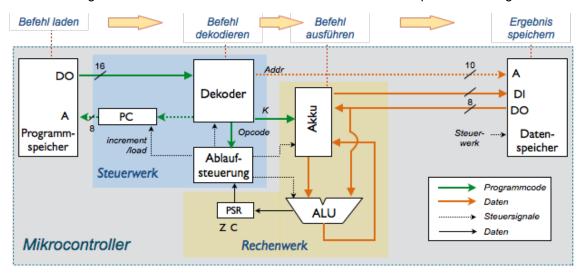

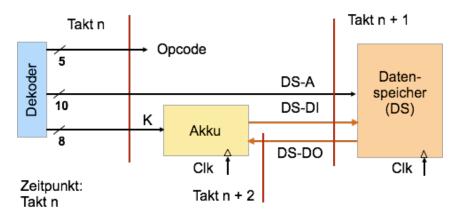

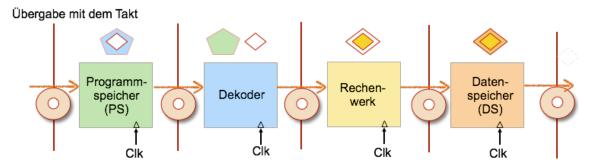

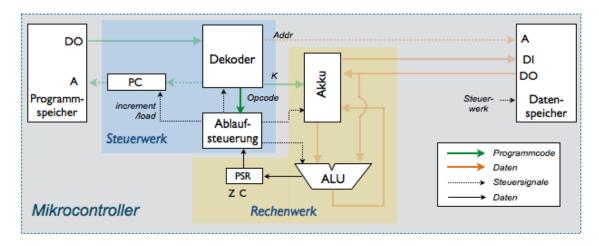

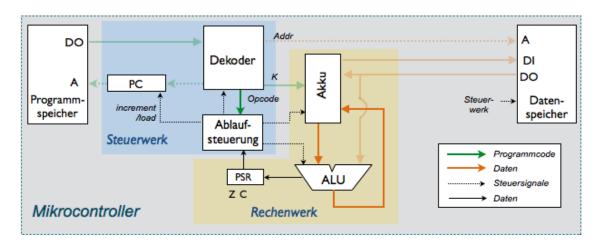

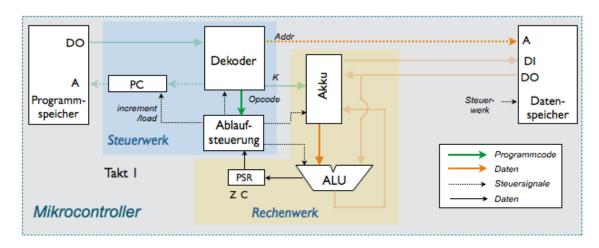

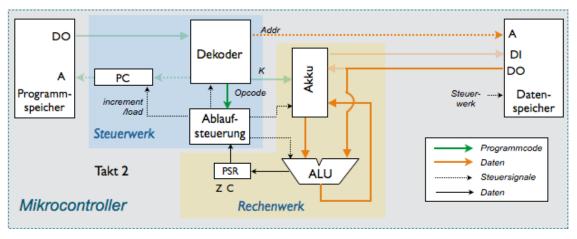

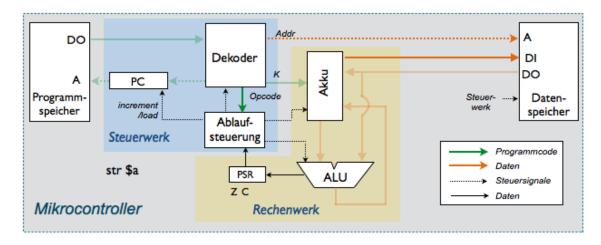

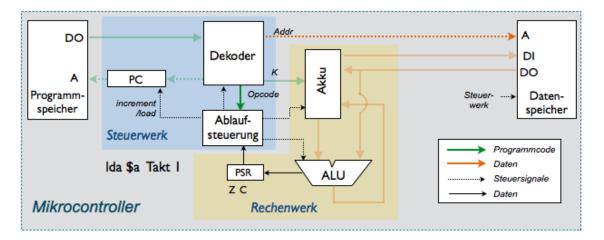

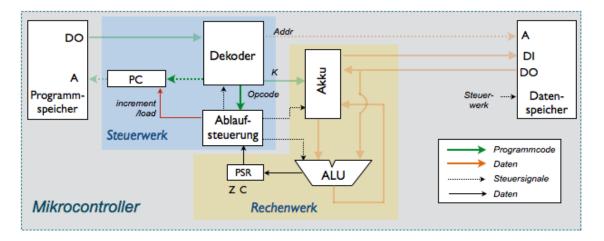

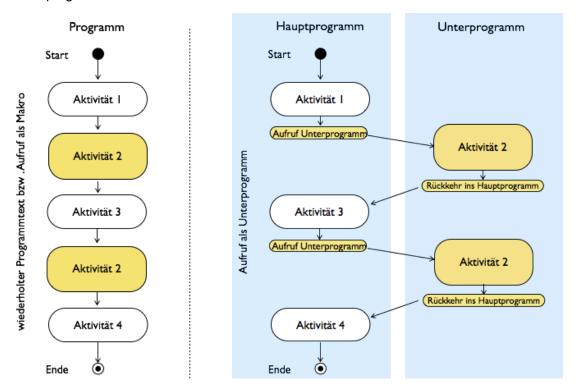

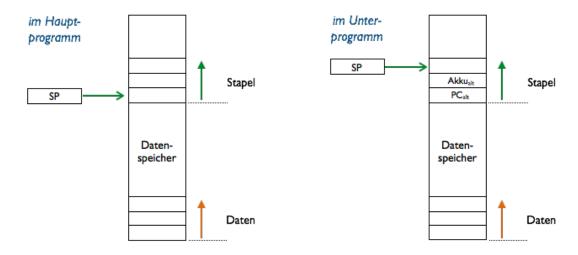

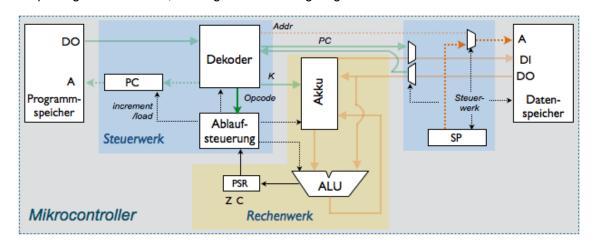

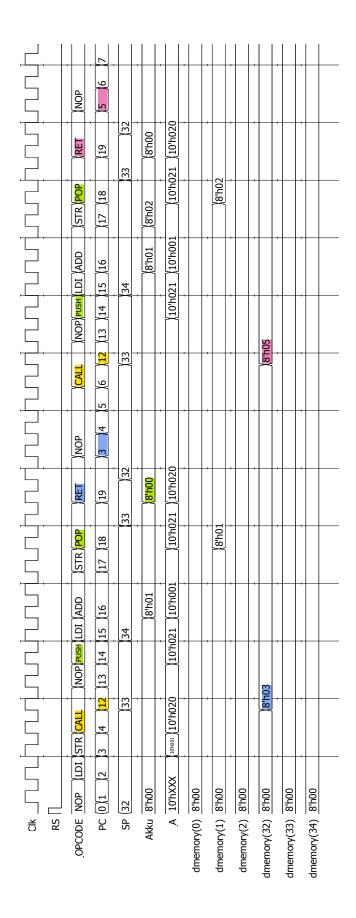

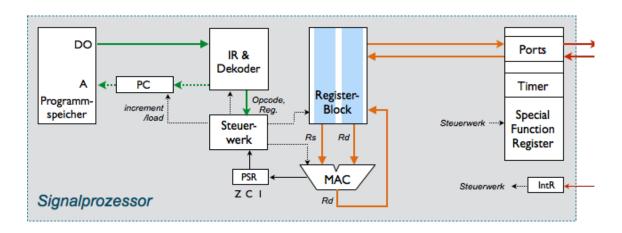

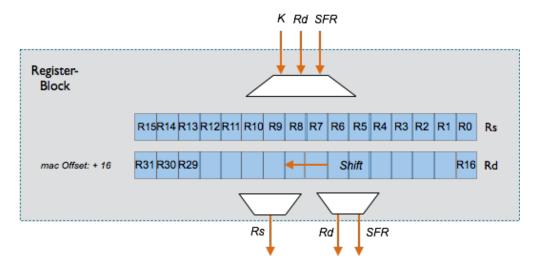

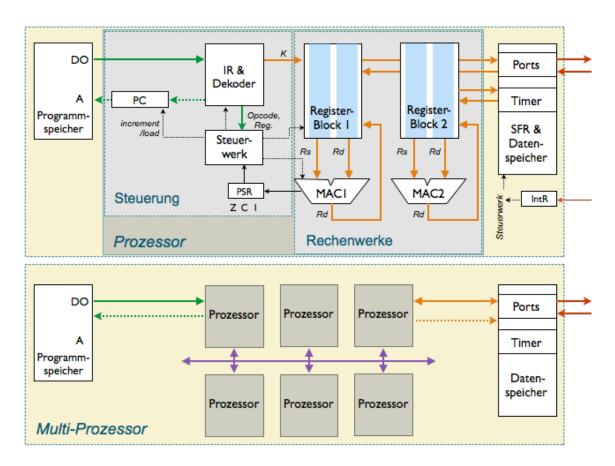

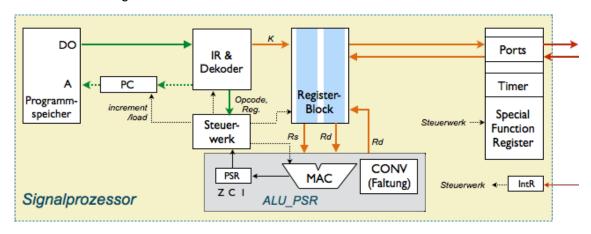

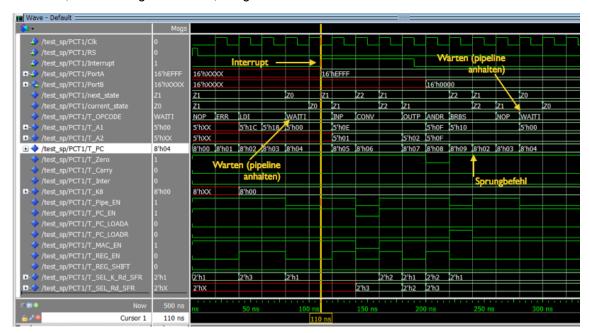

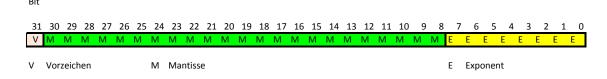

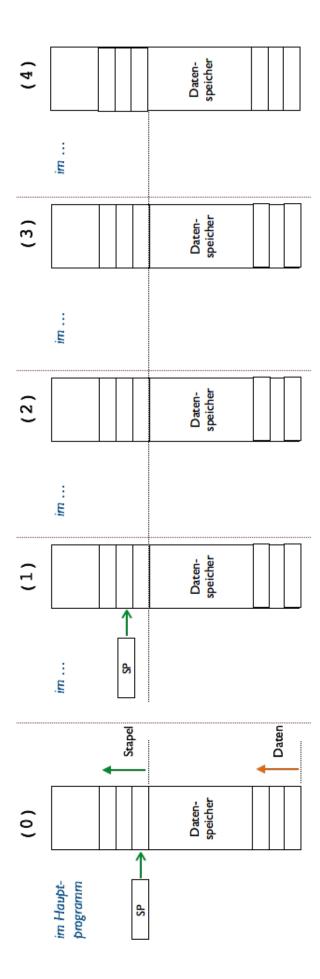

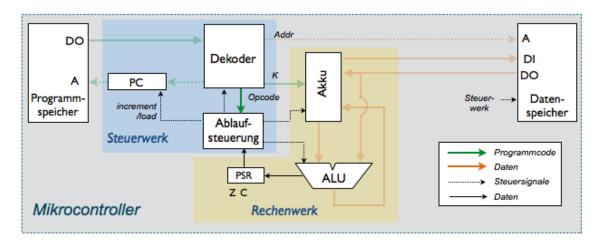

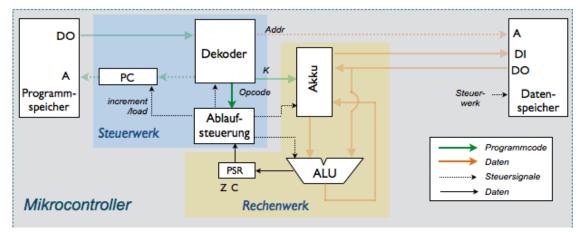

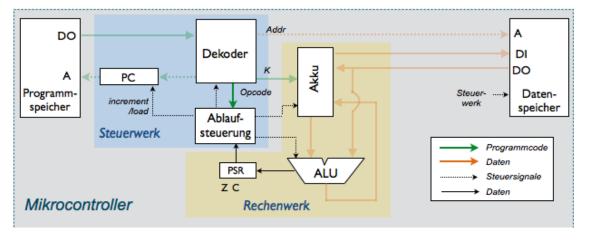

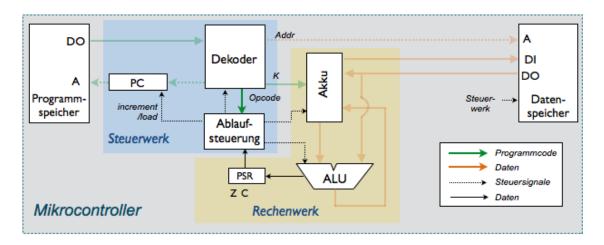

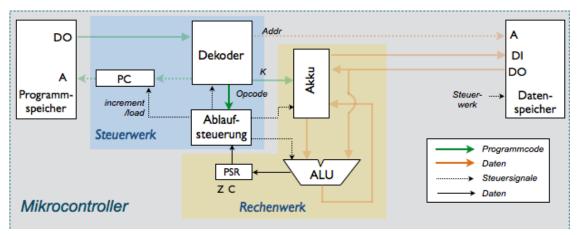

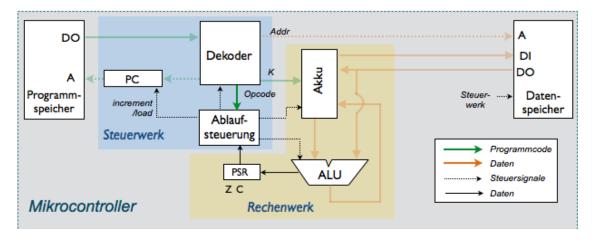

Die Schaltung bindet folgende Module ein: (1) die Memory-Einheit mit den beiden Speichern und der Logik, (2) die MAC-Einheit. Memory- und MAC-Einheit sind über interne Signale des Top-Moduls miteinander verbunden. Damit die Schaltung als Testprogramm eingesetzt werden kann, sind zunächst die externen Signale des Filters (Clk, RS, SR, XS und YN) noch nicht nach Außen geführt. Folgende Abbildung zeigt den Aufbau der Schaltung insgesamt.